◎ PCB設計技巧

◎ PCB Layout指南

◎ PCB的外型加工

◎ 芯片焊盤設計標準

◎ Via孔的作用及原理

◎ 如何在PCB設計中合理布置各元件

◎ PCB一般驗收標準

◎ PCB目檢檢驗規范

◎ PCB設計指引

◎ Cadence Allegro 簡介與安裝方法

◎ Mentor PADS2005 安裝方法

◎ 印制電路板的可靠性設計-地線設計

◎ Cadence Allegro 簡介與安裝方法

◎ Mentor PADS2005 安裝方法

◎ OrCAD 10.5 簡介與安裝

◎ Mentor WG/EN2004 安裝說明

◎ Protel DXP 2004 簡介與安裝]]>

| 下載信息 [文件大小: 下載次數: ] | |

點擊瀏覽該文件:“cadence仿真”高級研修班.rar 點擊瀏覽該文件:“cadence仿真”高級研修班.rar |

<p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt; LINE-HEIGHT: 13pt; mso-line-height-rule: exactly;"><b style="mso-bidi-font-weight: normal;"><span style="FONT-SIZE: 14pt; COLOR: black; FONT-FAMILY: 宋體;">一、<span style="mso-bidi-font-weight: bold;">培訓時間、地點<span lang="EN-US">:</span></span></span></b><span lang="EN-US" style="FONT-SIZE: 14pt; COLOR: black; FONT-FAMILY: 宋體;">2天,上海 2009年8月29-30日,8月28日報到;<b style="mso-bidi-font-weight: normal;">

</b></span>

<p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt; LINE-HEIGHT: 13pt; mso-line-height-rule: exactly;"><b style="mso-bidi-font-weight: normal;"><span style="FONT-SIZE: 14pt; COLOR: black; FONT-FAMILY: 宋體;">二、<span style="mso-bidi-font-weight: bold;">課程提綱:<span lang="EN-US">

</span></span></span></b>

<table cellspacing="0" cellpadding="0" width="665" align="left" border="1" style="BORDER-RIGHT: medium none; BORDER-TOP: medium none; BORDER-LEFT: medium none; WIDTH: 498.6pt; BORDER-BOTTOM: medium none; BORDER-COLLAPSE: collapse; mso-border-alt: solid windowtext .5pt; mso-table-lspace: 9.0pt; mso-table-rspace: 9.0pt; mso-table-anchor-vertical: paragraph; mso-table-anchor-horizontal: margin; mso-table-left: -3.65pt; mso-table-top: 4.7pt; mso-padding-alt: 0cm 5.4pt 0cm 5.4pt;"><tbody><tr style="HEIGHT: 15.2pt;"><td valign="top" width="319" style="BORDER-RIGHT: windowtext 0.5pt solid; PADDING-RIGHT: 5.4pt; BORDER-TOP: windowtext 0.5pt solid; PADDING-LEFT: 5.4pt; PADDING-BOTTOM: 0cm; BORDER-LEFT: windowtext 0.5pt solid; WIDTH: 239.4pt; PADDING-TOP: 0cm; BORDER-BOTTOM: windowtext 0.5pt solid; HEIGHT: 15.2pt; BACKGROUND-COLOR: transparent;"><p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt; LINE-HEIGHT: 13pt; mso-line-height-rule: exactly; mso-element: frame; mso-element-frame-hspace: 9.0pt; mso-element-wrap: around; mso-element-anchor-vertical: paragraph; mso-element-anchor-horizontal: margin; mso-element-left: -3.6pt; mso-element-top: 4.7pt; mso-height-rule: exactly;"><b style="mso-bidi-font-weight: normal;"><span lang="EN-US" style="FONT-SIZE: 14pt; FONT-FAMILY: 新宋體; mso-bidi-font-family: 宋體-18030;">

</span></b>

<p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt; LINE-HEIGHT: 13pt; mso-line-height-rule: exactly; mso-element: frame; mso-element-frame-hspace: 9.0pt; mso-element-wrap: around; mso-element-anchor-vertical: paragraph; mso-element-anchor-horizontal: margin; mso-element-left: -3.6pt; mso-element-top: 4.7pt; mso-height-rule: exactly;"><b style="mso-bidi-font-weight: normal;"><span style="FONT-SIZE: 14pt; FONT-FAMILY: 新宋體; mso-bidi-font-family: 宋體-18030;">第一天上午:<span lang="EN-US">

</span></span></b>

<p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt; TEXT-INDENT: 7pt; LINE-HEIGHT: 13pt; mso-line-height-rule: exactly; mso-element: frame; mso-element-frame-hspace: 9.0pt; mso-element-wrap: around; mso-element-anchor-vertical: paragraph; mso-element-anchor-horizontal: margin; mso-element-left: -3.6pt; mso-element-top: 4.7pt; mso-height-rule: exactly; mso-char-indent-count: .5; mso-char-indent-size: 14.0pt;"><span lang="EN-US" style="FONT-SIZE: 14pt; FONT-FAMILY: 新宋體; mso-bidi-font-family: 宋體-18030;">1、高速設計與PCB仿真流程;

</span>

<p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt; TEXT-INDENT: 7pt; LINE-HEIGHT: 13pt; mso-line-height-rule: exactly; mso-element: frame; mso-element-frame-hspace: 9.0pt; mso-element-wrap: around; mso-element-anchor-vertical: paragraph; mso-element-anchor-horizontal: margin; mso-element-left: -3.6pt; mso-element-top: 4.7pt; mso-height-rule: exactly; mso-char-indent-count: .5; mso-char-indent-size: 14.0pt;"><span lang="EN-US" style="FONT-SIZE: 14pt; FONT-FAMILY: 新宋體; mso-bidi-font-family: 宋體-18030;">2、Cadence 工具簡介;

</span>

<p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt; TEXT-INDENT: 7pt; LINE-HEIGHT: 13pt; mso-line-height-rule: exactly; mso-element: frame; mso-element-frame-hspace: 9.0pt; mso-element-wrap: around; mso-element-anchor-vertical: paragraph; mso-element-anchor-horizontal: margin; mso-element-left: -3.6pt; mso-element-top: 4.7pt; mso-height-rule: exactly; mso-char-indent-count: .5; mso-char-indent-size: 14.0pt;"><span lang="EN-US" style="FONT-SIZE: 14pt; FONT-FAMILY: 新宋體; mso-bidi-font-family: 宋體-18030;">3、Ibis模型解讀以及如何自制模型;

</span>

<p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt; TEXT-INDENT: 7pt; LINE-HEIGHT: 13pt; mso-line-height-rule: exactly; mso-element: frame; mso-element-frame-hspace: 9.0pt; mso-element-wrap: around; mso-element-anchor-vertical: paragraph; mso-element-anchor-horizontal: margin; mso-element-left: -3.6pt; mso-element-top: 4.7pt; mso-height-rule: exactly; mso-char-indent-count: .5; mso-char-indent-size: 14.0pt;"><span lang="EN-US" style="FONT-SIZE: 14pt; FONT-FAMILY: 新宋體; mso-bidi-font-family: 宋體-18030;">4、用作仿真實例的某網絡處理器高速單板情況介紹; 案例分析

</span>

<p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt; LINE-HEIGHT: 13pt; mso-line-height-rule: exactly; mso-element: frame; mso-element-frame-hspace: 9.0pt; mso-element-wrap: around; mso-element-anchor-vertical: paragraph; mso-element-anchor-horizontal: margin; mso-element-left: -3.6pt; mso-element-top: 4.7pt; mso-height-rule: exactly;"><b style="mso-bidi-font-weight: normal;"><span style="FONT-SIZE: 14pt; FONT-FAMILY: 新宋體; mso-bidi-font-family: 宋體-18030;">第一天下午:<span lang="EN-US">

要下載EDA360展望論文,請訪問 http://www.eda360.com .

改變的必要性

雖然消費者對高級移動計算設備與其他高性能電子設備的需求非常驚人,這些產品的開發方式正在扼殺當今技術所能實現的創新。根據傳統的垂直分工式開發方法,首先開發的是硬件與操作系統(OS),然后添加應用程序。硬件與操作系統完全集成后,應用程序被限制于基本的軟硬件平臺之中。

此外,老牌的電子公司正受到新進企業的強力挑戰:他們正在改變游戲規則,注重創新與應用程序的差異化。如今這些新進企業要求半導體供應商提供“適宜應用程序”的平臺,硬件與軟件都要適合特定的應用,例如移動計算。EDA360在產業體系內直接應對這種轉型,提出了一種應用驅動式開發模式,硬件是為動態滿足應用程序的需要而設計和開發的。

“作為一家從事產業經濟與技術轉型企業的創始人,我們為數以百萬計的人群提供機遇,我一直都在觀察其他人的舉動,”One Laptop per Child(每個兒童一臺筆記本電腦)公司創始人兼主席Nicholas Negroponte說。“Cadence擁有可能轉變微處理器產業乃至消費電子的經濟和表現的愿景和模式。EDA360明確指出了一個值得關注的遠景。”

立即行動起來:Cadence拓展合作,推出支持EDA360的新產品

為支持該業界遠景,Cadence今天還公布了實現EDA360的初步舉措——擴展技術合作,推出新產品系列,促進該技術在設計中的廣泛采用,并開發創新設備。這些舉措包括:

系統實現的體系式方法

由于應用導向型系統設計讓用戶能夠解決極其復雜與困難的任務,沒有哪家公司能夠提供所有必要的工具完全整合系統的硬件與軟件組件。EDA360的一個關鍵原則是需要一個體系,能夠讓客戶在面臨當前與未來市場的必然挑戰時受益。作為EDA360條款中關于“系統實現”這一承諾的第一步,Cadence與Wind River今天宣布進行技術合作,目標是整合Cadence Incisive Software Extensions和Wind River的Simics虛擬平臺。在尚無硬件可用之前,這種合作方式預計可讓工程師在虛擬平臺上開發電子設計 ,并且提高系統工程師在規劃、管理、激勵、檢查與監控不同軟硬件用例方面的效率。這種程度的合作對于提高系統級進度可預測性方面至關重要,同時可以降低風險,這是Cadence系統實現體系中未來多宗合作投資的第一步。

“電子產業需要適應新局勢才能繼續其過去30多年來的激進創新,”Wind River首席戰略官兼Simics部門總經理Vincent Rerolle說。“一種合作型體系式方法,讓設計團隊能夠挑選最適合其特定需要的組件,這是實現開放式標準型解決方案的必要要求,能夠解決成本問題,將利潤最大化。Cadence系統型產品與Simics的結合為系統開發的所有方面提供了一個真實的虛擬平臺。”

Cadence驗證計算平臺

星期一,公司公布了業界第一個完全集成的高性能驗證計算平臺,名為Palladium XP,它在一個統一的驗證環境中集成了模擬、加速與仿真。這種高度可擴展的Palladium XP驗證計算平臺是為了支持下一代設計而開發的,讓設計與驗證團隊能夠更快地完善他們的軟硬件環境,在更短的時間內生產出更高質量的嵌入式系統。

Cadence? Palladium? XP 最高支持20億門的設計結構,提供的性能最高可達4MHz并支持最多512名用戶同時使用。該平臺還提供了獨特的系統級解決方案,包括低功耗分析與指標驅動式驗證。

Palladium XP驗證計算平臺為開發者提供了其設計的高保真描繪(high-fidelity representation),讓他們能夠迅速而有把握地找到并修復錯誤,從而得到更高質量的IP、子系統、SoC和系統。設計團隊可以根據需要在可擴展的驗證環境中將模擬與加速和仿真進行“熱交換(hot-swap)”,這樣可以加快驗證過程,并且可以更早地測試嵌入式軟件,并且評估不同IP與系統架構的性能推斷。

“今天,半導體公司必須要同時擅長于軟硬件,而那些無法超越傳統由摩爾定律驅動的創新將會受到極大的沖擊,”Cadence總裁兼首席執行官Lip-Bu Tan說。“EDA360是整個產業的行動倡議。我們的客戶正面臨陌生的、極其復雜的挑戰,我們必須合作以提供能確保成功的先進技術與解決方案。因此,Cadence將會執行基于深厚客戶伙伴關系的EDA360戰略,以解決我們行業所面臨

]]>Cadence OrCAD 15.7,

讓PCB的設計進入更細節階段。與PSpice結合可應用于在Allegro平臺上。此套組系為一完整涵蓋前端至后端、使用微軟視窗平臺的流程,可以供印刷電路板(PCB)

設計師透過工具整合與程式自動化改善生產力與縮段進入市場的時間。 Orcad Unison Suite

整合了四種新近加強型的產品,在單一套裝軟體當中即可提供設計師所需的所有工具。

OrCAD 15.7 包括供設計輸入的Orcad CaptureR ,供類比與混合訊號模擬用的 PSpiceR A/D

Basics,供電路板設計的 Orcad LayoutR 以及供高密度電路板自動繞線的SPECCTRAR

4U。新加入的SPECCTRA,用以支援設計日益復雜的各種高速、高密度印刷電路板設計。SPECCTRA

提供設計師一種以形狀為基礎的,功能強大的繞線器,可在減少使用者介入情況下完成各種復雜設計。

OrCAD PCB Design Tools

The Cadence OrCAD product line includes affordable, high-performance

PCB design tools that boost productivity for smaller design teams

and individual PCB designers.

To stay competitive in today's market, engineers must take a design

from engineering through manufacturing with shorter design cycles

and faster time to market. To be successful, you need a set of

powerful, intuitive, and integrated tools that work seamlessly

across the entire design flow.

Cadence OrCAD personal productivity tools (including Cadence PSpice)

have a long history of addressing these demands. Designed to boost

productivity for smaller design teams and individual PCB designers,

OrCAD PCB design suites grow with your needs and technology

challenges. The powerful, tightly integrated PCB design suites

include design capture, librarian tools, a PCB editor, an

auto/interactive router, and optional analog and mixed-signal

simulator.

The affordable, high-performance OrCAD product line is easily

scalable with the full complement of Cadence Allegro PCB solutions.

The OrCAD product line is supported by a worldwide network of

Cadence Channel Partners. For sales, technical support, and training

inquiries please visit the global Cadence Channel Partner listing to

find a partner in your region.]]>

OrCAD PCB Designer with PSpice,Full featured suites with time-proven and new OrCAD technology,全功能增強套件,具有記時驗證功能以及新OrCAD技術!是目前為止OrCAD功能最強大的一個版本。

Cadence OrCAD 16.0, 讓PCB的設計進入更細節階段。與PSpice結合可應用于在Allegro平臺上。此套組系為一完整涵蓋前端至后端、使用微軟視窗平臺的流程,可以供印刷電路板(PCB) 設計師透過工具整合與程式自動化改善生產力與縮段進入市場的時間。 Orcad Unison Suite 整合了四種新近加強型的產品,在單一套裝軟體當中即可提供設計師所需的所有工具。組合各項產品的本套組定價US$5,995 (參考用), 比分別購買單項產品可節省一半以上的費用。

OrCAD 16.0 包括供設計輸入的Orcad CaptureR ,供類比與混合訊號模擬用的 PSpiceR A/D Basics,供電路板設計的 Orcad LayoutR 以及供高密度電路板自動繞線的SPECCTRAR 4U。新加入的SPECCTRA,用以支援設計日益復雜的各種高速、高密度印刷電路板設計。SPECCTRA 提供設計師一種以形狀為基礎的,功能強大的繞線器,可在減少使用者介入情況下完成各種復雜設計。

該公司CadenceR PCB系統部們的策略行銷部副總裁Jamie Metcalfe表示"Cadence OrCAD Suite 10.5提供一些了不起的科技,而售價是個人工程師設計市場中每一位都能負擔得起的。藉著發行此一軟體,本公司為此一市場區隔中的價格/性能制定了新的標準"。

Cadence OrCAD Suite With PSpice V10.5新功能關鍵更新:

OrCAD Capture, 具有快捷、通用的設計輸入能力,使OrCAD Capture原理圖輸入系統成為全球范圍內廣受歡迎 的設計輸入工具。它針對設計一個新的模擬電路、修改現有的一個PCB的原理圖,或者繪制一個HDL模塊的方框 圖,都提供了你所需要的全部功能,并且可以迅速地驗證你的設計。OrCAD Capture作為設計輸入工具,它運行在PC平臺,用于FPGA、PCB和PSpice設計應用中。它是業界第一個真正基于Windows環境的原理圖輸入程序。Capture易于使用的功能和特點使其已經成為了原理圖輸入的工業標準。

OrCAD PCB Editor, 聰明的布線環境, 方便的生產接口,OrCAD PCB Editor是OrCAD PCB Designer最主要和最強大的核心工具,也是由世界最先進的Cadence / Allegro電路板設計系統所研發. OrCAD PCB Editor 是一個用來建立及繪制復雜多層的電路板設計平臺. 而可擴張的功能選項使他對于現今市面上的設計及生產需求都能夠和完全符合.并能安心面對未來的挑戰。

SPECCTRA for OrCAD , SPECCTRA 是市面上最先進的自動及手動布線軟件.他能夠與OrCAD PCB Editor充分結合, 您能將電路板甚至是線路圖上所定義的參數及設計宣告傳導至SPECCTRA. 內建的自動布線軟件的可同時6 個訊號層走線而零件接點數不限, 如果你要的同時自動布線的層數較多,您可以用相當經濟的價格升級到 其它的等級得到最大的效益。

PSpice A/D (included in OrCAD with PSpice v16.0) PSpice 是一個全功能的模擬與混合信號仿真器,它支持從高頻系統到低功耗IC設計的電路設計。PSpice的仿真工具已和 OrCAD Capture及Concept HDL電路編輯工具整合在一起,讓工程師方便地在單一的環境里建立設計、控制模擬及得到結果。

Cadence該公司在華盛頓瑞吉菲德的一位作印刷電路板試計的顧問 (產品上市前 作第二階段貝塔測) Kris Nelson認為"OrCAD 16.0中的四層板SPECCTRA 自動繞線器使我能夠解決了在中小型設計中在高密度高精度繞線時所面臨的問題。Orcad Layout 與 SPECCTRA之間一次按鍵即可操控的介面,可執行雙向轉譯步驟的自動化步驟,確實省下我很多時間。 再加上此套組在各種工具之間提供完整的前、後(反)標注,使我再也不用為了想到作廢的電路板而難以入眠。"

::::::English Description::::::

The Cadence OrCAD product line includes affordable, high-performance PCB design tools that boost productivity for smaller design teams and individual PCB designers.To stay competitive in today’s market, engineers must take a design from engineering through manufacturing with shorter design cycles and faster time to market. To be successful, you need a set of powerful, intuitive, and integrated tools that work seamlessly across the entire design flow.

Cadence? OrCAD? personal productivity tools (including Cadence? PSpice?) have a long history of addressing these demands. Designed to boost productivity for smaller design teams and individual PCB designers, OrCAD PCB design suites grow with your needs and technology challenges. The powerful, tightly integrated PCB design suites include design capture, librarian tools, a PCB editor, an auto/interactive router, and optional analog and mixed-signal simulator.

The affordable, high-performance OrCAD product line is easily scalable with the full complement of Cadence? Allegro? PCB solutions.

The OrCAD product line is supported by a worldwide network of Cadence Channel Partners. For sales, technical support, and training inquiries please visit the global Cadence Channel Partner listing to find a partner in your region.To stay competitive in today’s market, engineers must take a design from engineering through manufacturing with shorter design cycles and faster time to market. To be successful, you need a set of powerful, intuitive, and integrated tools that work seamlessly from start to finish.

Cadence? OrCAD? personal productivity tools (including Cadence PSpice?) have along history of addressing these demands. Designed to boost productivity for smaller design teams and individual PCB designers, OrCAD PCB design suites grow with your needs and technology challenges. The powerful, tightly integrated PCB design suites include design capture, librarian tools, a PCB editor, an auto/interactive router, and optional analog and mixed-signal simulator. The affordable, high-performance OrCAD product line is easily scalable with the full complement of Cadence Allegro? PCB design technologies.

All OrCAD 16.0 products are now supported in Windows Vista? Enterprise.

New Cadence OrCAD and PSpice Bundle!

Cadence OrCAD EE Designer Plus

OrCAD EE Designer Plus provides powerful schematic entry and simulation in one premium package. This competitively priced, complete front-end design solution includes:

OrCAD Capture schematic entry, the world’s leading schematic capture tool

PSpice A/D for analog and mixed-signal simulation

PSpice advanced analysis capabilities—sensitivity analysis, optimization, Smoke (stress analysis), and Monte Carlo (yield analysis)—to automatically maximize the performance of circuits

For more information contact us at info@ema-eda.com or call 800-813-7494.

Cadence OrCAD Capture

Improved support for complex hierarchical designs, including better support for occurrence properties and externally referenced designs.

Support for placing and moving text and drawing objects on fine grid independent of connectivity objects

Enhancements to archiving adds an option to include PSpice models in the archive libraries which improves the performance of archived simulation profiles

Improved error messages and DRC engine

Cadence Help Online Documentation System replaces CDSDoc, providing faster invocation time, advanced search capabilities, and built-in viewing window

Usability enhancements and implementation of over 100 CCRs for improved quality and performance

Cadence OrCAD Capture CIS Option

Support for including mechanical parts and assemblies in standard component information system (CIS) Bill of Materials (BOM)

Better support for Japanese characters in CIS

Better BOM generation for non-English operating systems

Cadence PSpice A/D

Improved speed for power electronics designs, especially those using ABM if-then expressions, which will simulate up to 50x faster

CheckPoint Restart feature allows you to save the state of a transient simulation at specific times as CheckPoints. Prior to restarting, you can change component values, so if you’re not getting the results you want, you can tune your circuit without having to restart from the beginning. This is particularly useful for circuits that have a long startup time like a switch mode power supply. You can simulate once to reach steady state, tune the circuit to get the final result you want, and then simulate from the beginning to verify the full simulation. In this situation, CheckPoint Restart can be a significant time saver

Autoconvergence feature allows PSpice to automatically modify convergence options as necessary. This reduces the need for user interaction for problem circuits

Improved transient convergence. Adaptive iteration, improvements in the step time algorithm, and an improved switch model allow PSpice to converge on certain types of problem circuits

Run in resume mode accessible from graphical user interface (GUI)

Minimum step size recalculation

Usability enhancements

Tasks such as adding a trace, adding a plot, zooming the view, or adding a text label are now available using the right mouse button to display a context-sensitive menu in the Probe window

Probe window cursors now display X and Y coordinates on the status bar of the Probe window

Improved simulation speed for E and G device-based circuits

PSpice libraries have 120 new power devices. Updated vendor libraries include 290 new LED models

Cadence Help Online Documentation System replaces CDSDoc, providing faster invocation time, advanced search capabilities, and built-in viewing window

Cadence PSpice AA

PSpice Advanced Analysis support for legacy PSpice models. Traditional tolerance specifications can now be used by the Monte Carlo and Sensitivity tools. This includes the use of PDF custom distributions and device and lot tolerances

Cadence OrCAD PCB Designer (including OrCAD PCB Editor)

OrCAD Layout translator user interface opens from within OrCAD PCB Editor

Cadence Help Online Documentation System replaces CDSDoc, providing faster invocation time, advanced search capabilities, and built-in viewing window

Usability enhancements made within the display canvas and to the command structure

Redesigned color / visibility GUI

Enhancements made to the underlying graphics system, based on OpenGL graphics engine

Physical and spacing constraints incorporated in the Allegro constraint management system

Interactive and automatic controls for component fanout (pin escaping)

Context-sensitive editing paradigm built on selecting database objects first, followed by action command

Cadence OrCAD Layout

Cadence Help Online Documentation System replaces CDSDoc, providing faster invocation time, advanced search capabilities, and built-in viewing window

Support for GerbTool Version 15.0

Implementation of numerous CCRs for improved quality and performance

Please note: The OrCAD 16.0 upgrade will be provided without charge to all current OrCAD customers with active maintenance contracts. If you haven’t received your updated license file and CD by July 23, 2007, or if you have additional questions, please

]]>Cadence 學習:

關于Cadence的書籍不是很多,我看了以下幾本:

1、《Cadence高速電路板設計與仿真》:書很厚,內容最全,但感覺很多直接翻譯Cadence的help文件,只講怎么操作,沒有講清楚為什么這么操作,我主要在里面學習了orCAD(CIS,orCAD 是后來被Cadence收購的,現在已經被Cadence整合進去,和其他軟件實現無縫連接)的基本操作。

2、《Cadence Concept HDL&&Allegro 原理圖和PCB設計》:EDA先鋒工作室出的書我一直認為是比較不錯的,這本也不例外,但是Cadence Concept HDL(HDL)這個原理圖設計工具感覺沒有orCAD(CIS)操作來的方便,所以我主要從這本書上學習了Allegro的操作,本書對Allegro的講解感覺比上一本書好理解。

3、《Cadence高速PCB設計與仿真分析》:Cadence功能強大,純粹的畫電路板功能只是其很小一部分功能,其還可以在高速電路設計,信號完整性(SI),電源完整性(PI)仿真等方面發揮強大的功能,這本書上涉及到一部分高速PCB仿真的內容,書的后面幾章講解model integrity(查看,編輯IBIS模型),PCB SI,SigXploer等工具。

4、 除了以上幾本書外,網上一直流傳著中興公司內部的Cadence培訓教程,共5個分冊:原理圖分冊,PCB設計分冊,約束管理器分冊,自動布線器分冊,仿真分冊,里面的講解也很詳細,很多內容都是直接從實際出發開始講解,需要的人可以給我留言,我會發給大家。

5、在Cadence的學習中感覺這幾個論壇不錯:

http://www.eda365.com/index.php

http://www.eda365.com/index.php

6、在Cadence的學習中我認為主要要把握一下幾點:

a、焊盤文件的建立(.pad),分清楚各種焊盤的區別,在各層中的結構,剛從protel直接轉型用Cadence,這一點一定要注意。下面給一張比較詳細的示意圖,便于大家理解

b、分清楚電路板上各個層的含義,一般兩層板都會有頂層(底層)絲印層(silk),頂層(底層)阻焊層(soldermask)(阻焊層即為在電路板上不刷那層綠油的層),頂層(底層)布線層(etch),其它層根據具體要求再設置。

c、Cadence的操作都是先選操作內容,再選操作對象,這一點剛開始很不習慣,用多了以后感覺這是它的一個優點。

d、遺憾的一點是Cadence輸出的鉆孔文件不支持橢孔(olong),主要自己畫多個圓過孔來模擬,不知道有沒有其他方法。

下面講講FPGA的學習:

講FPGA的學習之前不得不提硬件描述語言(HDL),我主要用的是Verilog語言,另外一種常用的就是VHDL語言,兩種語言各有優劣,對于Verilog的學習我主要推薦以下兩本書:

1、《verilog 數字系統設計教程》,這本書對于入門是一本很好的書,通俗易懂,讓人很快上手,它里面的例子也不錯。但本書對于資源優化方面的編程沒有多少涉及到。

2、《設計與驗證Verilog HDL》,這本書雖然比較薄,但是相當精辟,講解的也很深入,很多概念看了這本書有種豁然開朗的感覺,呵呵。

其實Verilog語言是相當容易上手的,主要是要建立一個硬件電路編程的概念,很多模塊都是并行的,而不是軟件編程中的串行。要先畫電路模塊方框圖再進行程序的編寫。

下面講講FPGA的學習,其實剛開始由于程序規模不是很大,我用的是CPLD(MAXII系列的),后來規模大了,尤其是AD高速緩存中要用到FIFO,CPLD中沒有RAM,所以自己又做了FPGA(cycloneII系列)的板子。其實MAXII系列和FPGA的內部結構已經很像了,都是基于LUT的。CPLD 和FPGA的界限也越來越模糊。FPGA學習中也主要看了兩本EDA先鋒工作室出的書:

1、《Altera FPGA/CPLD 設計(基礎篇)》:講解一些基本的FPGA設計技術,以及QuartusII中各個工具的用法(IP,RTL,SignalProbe,SignalTapII,Timing Closure Floorplan,chip Editor等),對于入門非常好。

2、《Altera FPGA/CPLD 設計(高級篇)》:講解了一些高級工具的應用,LogicLock,時序約束很分析,設計優化,也講述了一些硬件編程的思想,作為提高用。

3、《FPGA設計指南--器件,工具和流程》:這本書看了他的目錄忍不住就買了,這本書講述了FPGA設計的各個方面,雖然每個方面都是點到為止,但能讓你有個整體的概念,了解FPGA的所有設計功能,了解FPGA開發的整個流程。

4、FPGA的學習其實不難,剛開始看到他有這么多引腳,很多人就害怕,其實大部分引腳都是IO口,由你隨意定義,真正的控制及配置管腳很少,一般書上都會說明這些腳怎么連接,自己對照著畫個FPGA的板子,再在上面調試一些例程,這樣學起來還是很快的。下面曬一下我自己畫的FPGA開發板,FPGA是ep2c5,配置芯片是EPCS1,其實也不能叫做開發板,由于項目要求面積小,只接了幾個開關和LED,其他引腳全部用插針連出來了,比較失敗的是四個定位孔畫的太大了,呵呵

]]>

]]>Cadence獲得與在Cadence的產品系列中使用的IBM內部測試工具有關的知識產權(IP)。

Synopsys和National Semiconductor正合作開發支持其手持便攜式設備的PowerWise技術的參考設計流程。此流程基于Synopsys的Galaxy設計平臺,包括了Synopsys的合成工具和Avanti的布局與布線工具。這兩個公司已經合作開發了使用可變電源電壓設計的方法。 在這項合作中,Synopsys在Galaxy設計平臺中增加對可變電源電壓的支持,National Semiconductor提供使用Synopsys的Liberty格式的程序庫,以及關鍵的IP和測試案例。 ]]>

(一)、SKILL基礎

(二)、利用AXL接口操作Allegro PCB對象

(三)、注冊和使用自定義Allegro命令

(四)、Allegro UI界面設計和響應

Email: TrizDev@yahoo.cn (以前的郵箱丟了)

四、Allegro UI界面設計和響應

1、簡介

界面是交互設計中不可缺少的一部分,很多時候我們無法只讓程序孤芳自賞地運行

2、基于文本描述的SKILL界面設計

例子:Example.form(簡單的幾段文字已經勾勒出我們想要的界面)

FILE_TYPE=FORM_DEFN VERSION=2

FORM

FIXED

PORT 26 20

HEADER "FINDER..."

TILE

TEXT "COMPONENT LIST"

TLOC 1 1

FSIZE 25 3

ENDTEXT

FIELD Placed_List

FLOC 1 3

LIST "" 24 16

OPTION sort

ENDFIELD

FIELD done

FLOC 9 33

MENUBUTTON " OK " 10 3

ENDFIELD

ENDTILE

ENDFORM

3、測試Form的方法

Form測試接口函數axlFormTest(s_formPath)

示例:

axlFormTest("C:\\Example.form")

功能:

利用這個函數可以檢查Form文件的語法以及Form的顯示效果, 編輯界面時不斷使用,使你的界面更加漂亮

Tips:

A、Allegro所有的Form文件都放在Setup - User Preferences...菜單,選擇UI_Path列別中的formpath。

查看Allegro所有界面文件,很好的界面重用資源

B、將自定義的Form文件放在formpath下可以不用寫絕對路徑調用,不信試試

4、界面工具開發ABCDE

A、創建界面文件并使用axlFormCreate或axlMiniStatusLoad打開Form句柄(注意卸磨殺驢)

B、使用axlFormSetField初始化界面區域

C、axlFormDisplay顯示界面

D、在axlFormCallback中定義用戶交互和區域響應

E、使用axlFormClose關閉界面窗口

/*

功能:通過選擇界面列表框中的器件名稱瀏覽器件

命令:OverviewComps

*/

;注冊命令

axlCmdRegister("OverviewComps" 'TestFormAppMainModule)

;創建界面文件并顯示界面(主模塊)

procedure( TestFormAppMainModule()

prog( (FileName FilePort)

;寫文件生成界面文件

FileName = "TestForm.form"

FilePort = outfile(FileName "w")

fprintf(FilePort "FILE_TYPE=FORM_DEFN VERSION=2\n")

fprintf(FilePort "FORM\n")

fprintf(FilePort "FIXED\n")

fprintf(FilePort "PORT 26 20\n\n")

fprintf(FilePort "HEADER \"FORM TEST...\"\n\n")

fprintf(FilePort "TILE\n\n")

fprintf(FilePort "TEXT \"ComponentList:\"\n\n")

fprintf(FilePort "TLOC 1 1\n")

fprintf(FilePort "FSIZE 25 3\n")

fprintf(FilePort "ENDTEXT\n\n")

fprintf(FilePort "FIELD ComponentList\n")

fprintf(FilePort "FLOC 1 3\n")

fprintf(FilePort "LIST \"\" 24 16\n")

fprintf(FilePort "OPTION sort\n")

fprintf(FilePort "ENDFIELD\n\n")

fprintf(FilePort "FIELD Quit\n")

fprintf(FilePort "FLOC 9 33\n")

fprintf(FilePort "MENUBUTTON \"EXIT\" 10 3\n")

fprintf(FilePort "ENDFIELD\n\n")

fprintf(FilePort "ENDTILE\n\n")

fprintf(FilePort "ENDFORM\n\n")

close(FilePort)

;創建界面句柄,刪除界面文件(卸磨殺驢...)

fw = axlFormCreate(gensym() FileName '("E" "OUTER") 'TestFormAppCallBack t)

deleteFile(FileName)

;界面區域初始化

TestFormFieldInit(fw)

;顯示界面

axlFormDisplay(fw)

return(t)

))

;界面區域初始化

procedure( TestFormFieldInit(fw)

prog( (CompsNameList)

;獲取所有的器件名稱

CompsNameList = axlDBGetDesign()->components~>name

;設置器件列表區域

axlFormSetField(fw "ComponentList" CompsNameList)

return(t)

))

;界面區域響應回調函數

procedure( TestFormAppCallBack(fw)

prog( (CompName CompId)

case(fw->curField

("ComponentList"

CompName = fw->curValue

CompId = axlSelectByName("COMPONENT" CompName)

;定位到對象

axlZoomToDbid(CompId t)

;顯示對象詳細信息

axlShowObject(CompId)

)

("Quit"

;清理現場

axlClearSelSet()

axlSetFindFilter(?enabled "NOALL" ?onButtons "NOALL")

axlFormClose(fw)

)

)

return(t)

))

5、參考文檔

%CDSROOT%\doc

例子:

D:\DesignAdvance\Cadence\SPB_15.2\doc

參考手冊列表:

algroskill AXL接口函數參考手冊

Tips:

看看下面的路徑下是什么東西,保證樂死你... ...

%CDSROOT%\share\pcb\example\skill

6、課后習題

搞懂%CDSROOT%\share\pcb\example\skill路徑下所有的程序代碼,然后恭喜你入門了... ...

語言:英語

網址:http://www.cadence.com/products/pcb/pcb_design/pages/default.aspx

類別:PCB設計

Cadence? 是世界上最大的電子設計技術和配套服務的 EDA 供貨商之一。Cadence? Allegro? 則是 Cadence 推出的先進 PCB 設計布線工具。 Allegro 提供了良好且交互的工作接口和強大完善的功能,和它前端產品 Capture 的結合,為當前高速、高密度、多層的復雜 PCB 設計布線提供了最完美解決方案。

Allegro 擁有完善的 Constraint 設定,用戶只須按要求設定好布線規則,在布線時不違反 DRC 就可以達到布線的設計要求,從而節約了煩瑣的人工檢查時間,提高了工作效率!更能夠定義最小線寬或線長等參數以符合當今高速電路板布線的種種需求。

軟件中的 Constraint Manger提供了簡潔明了的接口方便使用者設定和查看 Constraint 宣告。它與Cadence? OrCAD? Capture 的結合讓 E.E. 電子工程師在繪制線路圖時就能設定好規則數據,并能一起帶到Allegro工作環境中,自動在擺零件及布線時依照規則處理及檢查,而這些規則數據的經驗值均可重復使用在相同性質的電路板設計上。

Allegro 除了上述的功能外,其強大的自動推擠 push 和貼線 hug 走線以及完善的自動修線功能更是給用戶提供極大的方便;強大的貼圖功能,可以提供多用戶同時處理一塊復雜板子,從而大大地提高了工作效率。或是利用選購的切圖功能將電路版切分成各個區塊,讓每個區塊各有專職的人同時進行設計 ,達到同份圖多人同時設計并能縮短時程的目的 。

用戶在布線時做過更名、聯機互換以及修改邏輯后,可以非常方便地回編到 Capture 線路圖中,線路圖修改后也可以非常方便地更新到 Allegro 中;用戶還可以在 Capture 與 Allegro 之間對對象的互相點選及修改。

對于業界所重視的銅箔的繪制和修改功能, Allegro 提供了簡單方便的內層分割功能,以及能夠對正負片內層的檢閱。對于鋪銅也可分動態銅或是靜態銅,以作為鋪大地或是走大電流之不同應用。動態銅的參數可以分成對所有銅、單一銅或單一對象的不同程度設定,以達到銅箔對各接點可設不同接續效果或間距值等要求,來配合因設計特性而有的特殊設定。

在輸出的部分,底片輸出功能包含 274D 、 274X 、 Barco DPF 、 MDA 以及直接輸出 ODB++ 等多樣化格式數據當然還支持生產所需的 Pick & Place 、NC Drill 和 Bare-Board Test 等等原始數據輸出。

Allegro 所提供的強大輸入輸出功能更是方便與其它相關軟件的溝通,例如 ADIVA 、 UGS(Fabmaster) 、 VALOR 、 Agilent ADS… 或是機構的 DXF 、 IDF……… 。

為了推廣整個先進 EDA 市場 ,Allegro 提供了 OrCAD Layout 、 PADS 、 P-CAD 等接口,讓想轉換 PCB Layout 軟件的使用者,對于舊有的圖檔能順利轉換至 Allegro 中。 Allegro 有著 操作方便,接口友好,功能強大,整合性好 等諸多優點,是一家公司投資 EDA 軟件的理想選擇

隨著人們對通信需求的不斷提高,要求信號的傳輸和處理的速度越來越快.相應的高速PCB的應用也越來越廣,設計也越來越復雜.高速電路有兩個方面的含義:一是頻率高,通常認為數字電路的頻率達到或是超過45MHz至50MHz,而且工作在這個頻率之上的電路已經占到了整個系統的三分之一,就稱為高速電路.另外從信號的上升與下降時間考慮,當信號的上升時間小于6倍信號傳輸延時時即認為信號是高速信號,此時考慮的與信號的具體頻率無關.

2 高速PCB設計的基本內容

高速電路設計在現代電路設計中所占的比例越來越大,設計難度也越來越高,它的解決不僅需要高速器件,更需要設計者的智慧和仔細的工作,必須認真研究分析具體情況,解決存在的高速電路問題.一般說來主要包括三方面的設計:信號完整性設計、電磁兼容設計、電源完整性設計.

2.1 信號完整性(signal integrity)設計

信號完整性是指信號在信號線上的質量.信號具有良好的信號完整性是指當在需要的時候,具有所必需達到的電壓電平數值.差的信號完整性不是由某一因素導致的,而是由板級設計中多種因素共同引起的.特別是在高速電路中,所使用的芯片的切換速度過快、端接元件布設不合理、電路的互聯不合理等都會引起信號的完整性問題.具體主要包括串擾、反射、過沖與下沖、振蕩、信號延遲等.

2.1.1 串擾(crosstalk)

串擾是相鄰兩條信號線之間的不必要的耦合,信號線之間的互感和互容引起線上的噪聲.因此也就把它分為感性串擾和容性串擾,分別引發耦合電流和耦合電壓.當信號的邊緣速率低于1ns時,串擾問題就應該考慮.如果信號線上有交變的信號電流通過時,會產生交變的磁場,處于磁場中的相鄰的信號線會感應出信號電壓.一般PCB板層的參數、信號線間距、驅動端和接收端的電氣特性及信號線的端接方式對串擾都有一定的影響.在Cadence的信號仿真工具中可以同時對6條耦合信號線進行串擾后仿真,可以設置的掃描參數有:PCB的介電常數,介質的厚度,沉銅厚度,信號線長度和寬度,信號線的間距.仿真時還必須指定一個受侵害的信號線,也就是考察另外的信號線對本條線路的干擾情況,激勵設置為常高或是常低,這樣就可以測到其他信號線對本條信號線的感應電壓的總和,從而可以得到滿足要求的最小間距和最大并行長度.

2.1.2 反射(reflection)

反射和我們所知道的光經過不連續的介質時都會有部分能量反射回來一樣,就是信號在傳輸線上的回波.此時信號功率沒有全部傳輸到負載處,有一部分被反射回來了.在高速的PCB中導線必須等效為傳輸線,按照傳輸線理論,如果源端與負載端具有相同的阻抗,反射就不會發生了.二者阻抗不匹配會引起反射,負載會將一部分電壓反射回源端.根據負載阻抗和源阻抗的關系大小不同,反射電壓可能為正,也可能為負.如果反射信號很強,疊加在原信號上,很可能改變邏輯狀態,導致接收數據錯誤.如果在時鐘信號上可能引起時鐘沿不單調,進而引起誤觸發.一般布線的幾何形狀、不正確的線端接、經過連接器的傳輸及電源平面的不連續等因素均會導致此類反射. 另外常有一個輸出多個接收,這時不同的布線策略產生的反射對每個接收端的影響也不相同,所以布線策略也是影響反射的一個不可忽視的因素.

2.1.3 過沖(overshoot)和下沖(undershoot)

過沖是由于電路切換速度過快以及上面提到的反射所引起的信號跳變,也就是信號第一個峰值超過了峰值或谷值的設定電壓.下沖是指下一個谷值或峰值.過分的過沖能夠引起保護二極管工作, 導致過早地失效,嚴重的還會損壞器件.過分的下沖能夠引起假的時鐘或數據錯誤.它們可以通過增加適當端接予以減少或消除.

2.1.4 振蕩(ringing)和環繞振蕩(rounding)

振蕩的現象是反復出現過沖和下沖.信號的振蕩和環繞振蕩由線上過度的電感和電容引起的接收端與傳輸線和源端的阻抗不匹配而產生的,通常發生在邏輯電平門限附近,多次跨越邏輯電平門限會導致邏輯功能紊亂.振蕩和環繞振蕩同反射一樣也是由多種因素引起的,振蕩可以通過適當的端接或是改變PCB參數予以減小,但是不可能完全消除.

在Cadence的信號仿真軟件中,將以上的信號完整性問題都放在反射參數中去度量.在接收和驅動器件的IBIS模型庫中,我們只需要設置不同的傳輸線阻抗參數、電阻值、信號傳輸速率以及選擇微帶線還是帶狀線,就可以通過仿真工具直接計算出信號的波形以及相應的數據,這樣就可以找出匹配的傳輸線阻抗值、電阻值、信號傳輸速率,在對應的PCB軟件Allegro中,就可以根據相對應的傳輸線阻抗值和信號傳輸速率得到各層中相對應信號線的寬度(需提前設好疊層的順序和各參數).選擇電阻匹配的方式也有多種,包括源端端接和并行端接等,根據不同的電路選擇不同的方式.在布線策略上也可以選擇不同的方式:菊花型、星型、自定義型,每種方式都有其優缺點,可以根據不同的電路仿真結果來確定具體的選擇方式.

2.1.5 信號延遲(delay)

電路中只能按照規定的時序接收數據,過長的信號延遲可能導致時序和功能的混亂,在低速的系統中不會有問題,但是信號邊緣速率加快,時鐘速率提高,信號在器件之間的傳輸時間以及同步時間就會縮短.驅動過載、走線過長都會引起延時.必須在越來越短的時間預算中要滿足所有門延時,包括建立時間,保持時間,線延遲和偏斜. 由于傳輸線上的等效電容和電感都會對信號的數字切換產生延遲,加上反射引起的振蕩回繞,使得數據信號不能滿足接收端器件正確接收所需要的時間,從而導致接收錯誤.在Cadence的信號仿真軟件中,將信號的延遲也放在反射的子參數中度量,有Settledelay、switchdelay、Propdelay.其中前兩個與IBIS模型庫中的測試負載有關, 這兩個參數可以通過驅動器件和接收器件的用戶手冊參數得到, 可以將它們與仿真后的Settledelay、Switchdelay加以比較,如果在Slow模式下得到的Switchdelay都小于計算得到的值,并且在Fast的模式下得到的Switchdelay的值都大于計算得到的值,就可以得出我們真正需要的兩個器件之間的時延范圍Propdelay.在具體器件布放的時候,如果器件的位置不合適,在對應的時延表中那部分會顯示紅色,當把其位置調整合適后將會變成藍色,表示信號在器件之間的延時已經滿足Propdelay規定的范圍了.

2.2 電磁兼容性(Electro Magnetic Compatibility)設計

電磁兼容包括電磁干擾和電磁忍受,也就是過量的電磁輻射以及對電磁輻射的敏感程度兩個方面. 電磁干擾有傳導干擾和輻射干擾兩種.傳導干擾是指以電流的形式通過導電介質把一個電網絡上的信號傳導到另一個電網絡,PCB中主要表現為地線噪聲和電源噪聲.輻射干擾是指信號以電磁波的形式輻射出去,從而影響到另一個電網絡.在高速PCB及系統設計中,高頻信號線、芯片的引腳、接插件等都可能成為具有天線特性的輻射干擾源.對EMC的設計根據設計的重要性可以分為四個層次:器件和PCB級設計,接地系統的設計,屏蔽系統設計以及濾波設計.其中的前兩個最為重要,器件和PCB級設計主要包括有源器件的選擇、電路板的層疊、布局布線等.接地系統的設計主要包括接地方式、地阻抗控制、地環路和屏蔽層接地等.在Cadence的仿真工具中,電磁干擾的仿真參數可以設置在X、Y、Z三個方向上的距離、頻率的范圍、設計余量、符合標準等.此仿真屬于后仿真,主要檢驗是否符合設計要求,因此,在做前期工作時,我們還需要按照電磁干擾的理論去設計,通常的做法是將控制電磁干擾的各項設計規則應用到設計的每個環節,實現在各個環節上的規則驅動和控制.

2.3 電源完整性(power integrity)設計

在高速電路中, 電源和地的完整性也是一個非常重要的因素, 因為電源的完整性和信號的完整性是密切相關的.在大多數情況下,影響信號畸變的主要原因是電源系統.如:地反彈噪聲太大、去耦合電容設計不合適、多電源或地平面地分割不好、地層設計不合理、電流分配不均等都會帶來電源完整性方面的問題,引起信號的畸變而影響到信號的完整性.解決的主要思路有確定電源分配系統,將大尺寸電路板分割成幾塊小尺寸板,根據地平面反彈噪聲(Ground Bounce)(簡稱地彈)確定去耦電容,以及著眼于整個PCB板考慮等幾個方面.

在電路中有大的電流涌動時會引起地彈,如大量芯片的輸出同時開啟時,將有一個較大的瞬態電流在芯片與板的電源平面流過,芯片封裝與電源平面的電感和電阻會引發電源噪聲,這樣會在真正的地平面上產生電壓的波動和變化,這種噪聲會影響其它元器件的動作.設計中減小負載電容、增大負載電阻、減小地電感、減少器件同時開關的數目均可以減少地彈.由于地電平面分割,例如地層被分割為數字地、模擬地、屏蔽地等,當數字信號走到模擬地線區域時,就會產生地平面回流噪聲.同時根據選用的器件不同,電源層也可能會被分割為幾種不同電壓層,此時地彈和回流噪聲更需特別關注.在電源完整性的設計中電源分配系統和去耦電容的選擇很重要.一般使得電源系統(電源和地平面)之間的阻抗越低越好.可以通過規定最大的電壓和電流變化范圍來確定我們希望達到的目標阻抗,然后通過調整電路中的相關因素使電源系統各部分的阻抗與目標阻抗逼近.對于去耦電容,必須考慮電容的寄生參數,定量的計算出去耦電容的個數以及每個電容的容值和具體放置位置,盡量做到電容一個不多,一個不少.在Cadence仿真工具中,將接地反彈稱為同步開關噪聲(Simultaneous switch noise)。在仿真時將電源間的寄生電感、電容和電阻, 以及器件封裝的寄生電感、電容和電阻都做考慮,結果比較符合實際情況.還可以根據系統使用的電路類型與工作頻率,設置好期望的相關指標參數后,計算出合適的電容大小以及最佳的布放位置,設計具有低阻抗的接地回路來解決電源完整性問題。

3 高速PCB的設計方法

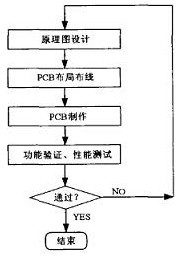

3.1 傳統的設計方法

如圖1是傳統的設計方法,在最后測試之前,沒有做任何的處理,基本都是依靠設計者的經驗來完成的.在對樣機測試檢驗時才可以查找到問題,確定問題原因.為了解決問題,很可能又要從頭開始設計一遍.無論是從開發周期還是開發成本上看,這種主要依賴設計者經驗的方法不能滿足現代產品開發的要求,更不能適應現代高速電路高復雜性的設計.所以必須借助先進的設計工具來定性、定量的分析,控制設計流程.

3.2 Cadence設計方法

現在越來越多的高速設計是采用一種有利于加快開發周期的更有效的方法.先是建立一套滿足設計性能指標的物理設計規則,通過這些規則來限制PCB布局布線.在器件安裝之前,先進行仿真設計.在這種虛擬測試中,設計者可以對比設計指標來評估性能.而這些關鍵的前提因素是要建立一套針對性能指標的物理設計規則,而規則的基礎又是建立在基于模型的仿真分析和準確預測電氣特性之上的,所以不同階段的仿真分析顯得非常重要.Cadence軟件針對高速PCB的設計開發了自己的設計流程,如圖2它的主要思想是用好的仿真分析設計來預防問題的發生,盡量在PCB制作前解決一切可能發生的問題.與左邊傳統的設計流程相比,最主要的差別是在流程中增加了控制節點,可以有效地控制設計流程.它將原理圖設計、PCB布局布線和高速仿真分析集成于一體,可以解決在設計中各個環節存在的與電氣性能相關的問題.通過對時序、信噪、串擾、電源結構和電磁兼容等多方面的因素進行分析,可以在布局布線之前對系統的信號完整性、電源完整性、電磁干擾等問題作最優的設計.

圖1 傳統高速設計流程

圖2 Cadence高速設計流程

4 結語

高速PCB設計是一個很復雜的系統工程,只有借助于那些不僅能計算設計中用到的每個元器件的物理特性和電氣特性的影響及其相互作用,還必須能從設計的PCB中自動提取和建立模型,并且具有提供對實際設計操作產生動態特性描述的仿真器等強大功能的EDA軟件工具,才能更全面地解決以上信號完整性、電磁干擾、電源完整性等問題.在具體設計過程中,在橫向上要求各部分的設計人員通力合作,在縱向上要求設計的各個階段綜合考慮,把設計和仿真貫穿于整個設計過程,實現過程的可控性,具體指標的量化.只有這樣才能做到高效的設計.

]]>全球電子設計創新領先企業Cadence設計系統公司,今天宣布推出其最新版Cadence? Allegro? 與 OrCAD?印刷電路(PCB) 軟件,它擁有的全新功能與特性能夠提高PCB工程師的績效與效率。Allegro與OrCAD PCB Design 16.3版本為PCB工程師帶來了極大的新優勢,包括改進終端產品小型化設計能力并減少原型機設計的反復次數,使得設計周期更具可預測性。

本版本包括一些新增功能和互連密度的改進,如剛柔布線,擴展的高密度互連(HDI)規則、PCB的三維(3D)顯示與RF電路的非對稱避讓。拓展的微孔疊層規則允許用戶創建極為復雜的HDI設計,而與柔性板輪廓吻合的多線式曲形總線布線會加快剛柔設計。此外,集成的3D PCB瀏覽器讓設計師可以看到元件與HDI微導孔內部,從而為機械設計團隊消除了不必要的迭代。Allegro PCB RF選件還通過使用一個或多個RF元件的非對稱避讓幫助工程師加快創建精確RF電路的速度。

“我們參與了16.3版本的多個階段的測試,對其印象非常深刻,” Kaleidescape Canada公司高級PCB設計師Vincent Di Lello說。“這個新版本的改良很好地解決了我們的小型化設計問題,我們期待著這個新版本發布后能夠盡快將其應用于我們的設計流程中。”

新版Allegro與OrCAD使用多階段預發布的方式確保內容與質量能夠符合客戶的需要。來自北美、歐洲、亞洲和日本的20多家客戶參與了多階段測試計劃。參與測試計劃的客戶與Cadence的合作伙伴包括NVIDIA、Emerson、Kaleidescape、Freedom CAD、NordCAD、FlowCAD、Graser與Tektronix。

16.3版本中還包含對OrCAD系列產品應用效率與可用性的一系列大幅改良。例如OrCAD Capture CIS如今提供了自動布線功能以迅速增加連線,還有全新的三維封裝顯示功能。OrCAD PCB Editor提供了三維查看與“翻板”設計/編輯以及單面PCB設計的跳線支持。OrCAD Signal Explorer有一個經改良的用戶界面,有拖拽和復制粘貼功能,有前后關聯的右擊功能并支持本地IBIS模型。

可用性改進是新版Allegro PCB信號與電源完整性軟件的又一個重點,它提供了一個全新的用戶界面,并為預布線分析環境增加了疊層感知功能。通過對本地IBIS與SPICE模型包括Cadence Virtuoso? Spectre? 電路仿真模型的支持, I/O緩沖器建模標準也包含在其中。另外一個改進設計周期管理的地方是能夠用大量吉比特級信號快速掃描PCB,并且迅速確定應該在哪里進行詳細分析,信號會根據其信噪比進行排列。

“這個最新版Allegro有很多的改進,能夠解決剛性或剛柔設計上的小型化設計問題,”Freedom CAD首席運營官Scott Miller說。“作為一家設計服務公司,我們一直很有興趣提高我們設計師的效率和設計周期的可預測性。我們將會轉移到16.3版本,也推薦我們的客戶盡快轉移。”

該版本解決的另外一些重要問題是與部件數據管理有關。集成的ECAD、MCAD部件創建,生成與發布可以降低不必要的原型機出樣次數。這個新部件導入功能可以擴展預發布與臨時部件的管理與通知,縮短設計周期。此外,工程師可以通過使用批準的與推薦的部件替換原來的部件來實現自動部件更新,也可以通過廢棄部件跟蹤以確保產品的質量。

Allegro與OrCAD PCB Design 16.3版將于2009年12月初開始向客戶提供下載。

]]>SPB15.2 CD1~3,安裝1、2,第3為庫,不安裝

License安裝:

設置環境變量lm_license_file D:Cadencelicense.dat

修改license中SERVER yyh ANY 5280為SERVER zeng ANY 5280

二、用Design Entry CIS(Capture)設計原理圖

進入Design Entry CIS Studio

設置操作環境OptionsPreferencses:

顏色:colors/Print

格子:Grid Display

雜項:Miscellaneous

.........常取默認值

配置設計圖紙:

設定模板:OptionsDesign Template:(應用于新圖)

設定當前圖紙OptionsSchematic Page Properities

創建新設計

創建元件及元件庫

FileNewLibrary(...Labrary1.OLB)

DesignNew Part...(New Part Properties)

Parts per 1/2/..(封裝下元件的個數)

Pakage Type:(只有一個元件時,不起作用)

Homogeneous:復合封裝元件中(多個元件圖組成時)每個元件圖都一樣(default適用于標準邏輯)

Heterogeneous:復合封裝元件(多個元件圖組成時)中使用不一樣的元件圖(較適用于大元件)

一個封裝下多個元件圖,以View ext part(previous part)切換視圖

Part Numbering:

Alphabetic/numeric

Place(PIN...Rectangle)

建立項目FileNewProject

Schematic ew page (可以多張圖:

單層次電路圖間,以相同名稱的“電路端口連接器”off-page connector連接

層次式電路圖:以方塊圖(層次塊Hierarchical Block...)來代替實際電路的電路圖,以相同名稱Port的配對內層電路,內層電路之間可以多張,同單層連接

繪制原理圖

放置元器件:Place

元件:Part(來自Libraries,先要添加庫)

電源和地(power gnd)

連接線路

wire

bus:與wire之間必須以支線連接,并以網標(net alias)對應(wire:D0,D1....D7;bus:D[0..7])

數據總線和數據總線的引出線必須定義net alias

修改元件序號和元件值

創建分級模塊(多張電路圖)

平坦式(單層次)電路:各電路之間信號連接,以相同名稱的off-page connector連接

層次式電路圖:以方塊圖(層次塊Hierarchical Block...)來代替實際電路的電路圖,以相同名稱Port的配對內層電路,內層電路之間可以多張,同單層連接

標題欄處理:

一般已有標題欄,添加:PlaceTitle Block()

PCB層預處理

元件的屬性

編輯元件屬性

在導入PCB之前,必須正確填寫元件的封裝(PCB Footprint)

參數整體賦值(框住多個元件,然后Edit Properties)

分類屬性編輯

Edit PropertiesNew ColumnClass:IC(IC,IO,Discrete三類,在PCB中分類放置)

放置定義房間(Room)

Edit PropertiesNew ColumnRoom

添加文本和圖像

添加文本、位圖(Place...)

原理圖繪制的后續處理(切換到項目管理器窗口,選中*.DSN文件,然后進行后處理————DRC檢查、生成網表及元器件清單)

設計規則檢查(ToolsDesign Rules Check...)

Design Rules Check

scope(范圍):entire(全部)/selection(所選)

Mode(模式):

occurences(事件:在同一繪圖頁內同一實體出現多次的實體電路)

instance(實體:繪圖頁內的元件符號)

如一復雜層次電路,某子方塊電路重復使用3次,就形成3次事件;子方塊電路內本身的元件則是實體。

Action(動作):check design rules/delete DRC

Report(報告):

Create DRC markers for warn(在錯誤之處放置警告標記)

Check hierarchical port connection(層次式端口連接)

Check off-page connector connection(平坦式端口連接)

Report identical part referenves(檢查重復的元件序號)

Report invalid package (檢查無效的封裝)

Report hierarchical ports and off-page connector(列出port和off-page 連接)

Check unconnected net

Check SDT compatible

Report all net names

View output

ERC Matrix

元件自動編號(ToolsAnnotate)

scope:Update entire design/selection

Action;

Incremental/unconfitional reference update

reset part reference to "?"

Add/delete Intersheet Reference(在分頁圖紙的端口的序號加上/刪除圖紙的編號)

Combined property

Reset reference numbers to begin at 1 each page

Do not change the page number

自動更新器件或網絡的屬性(ToolsUpdate Properties...)

scope:Update entire design/selection

Action:

use case inseneitive compares

convert the update property to uppercase

ynconditionally update the property

Do not change updated properties visibility

Cadence表示,典型高速板設計中受約束線網的數量已經從占總線網的25%激增到75%以上。設計隊伍中SI工程師的任務是分析這些線網。但是, 隨著需要分析的板上線網數量及新芯片復雜性的快速增加,這種任務也在快速增加。由于允許電氣工程師無需依賴SI工程師分析所有受約束線網即可開發并管理其設計中的約束,因此SPECCTRAQuest EE支持的新的設計方法,提高了設計隊伍的效率,降低對任務繁重的SI工程師的依賴,通過使電氣工程師能夠開發和管理他們設計中的電氣規則而不需依靠SI工程師分析所有需要規則約束的網絡,將能夠很好地控制附加成本。

據介紹,現在設計團隊必須確定受約束的網點并把它們分成兩組:設計循環所必需且需要SI快速驗證的網點,以及不重要的、無需驗證的網點。這種實踐通常意味著要么過渡約束那些不太重要的網點,要么根本不進行控制,因此會提高電路板的成本。當通過這種方式管理關鍵網點時,電路板出故障的風險會增加,從而造成不可避免的昂貴的重復流片。SPECCTRAQuest EE使電氣工程師能夠確定前端不太關鍵的網點的最佳約束,同時SI工程師也能夠把注意力集中到新的芯片組和非常關鍵的網點,從而節省時間和資金。

SPECCTRAQuest EE作為仿真工具包,包含了分級約束管理器(Constraint Manager)及SigXplorer圖形化拓撲,另外還與完整的Cadence約束驅動的高速設計流程緊密集成,其包含用于高速設計及分析的SPECCTRAQuest SI Expert、用于圖形輸入的Concept HDL、用于布線的Allegro、用于自動布線的SPECCTRA、以及用于定義、管理和驗證整個流程中約束的Constraint Manager。采用SigXplorer的電氣工程師和SI工程師可以實時共享約束模板,包括用于主動、動態協作的復雜拓撲開發,分析。SPECCTRAQuest EE還為電氣工程師提供新的SI分析方法指南,使他們能夠快速開始約束開發。

]]>

Cadence公布了Virtuoso Multi-Mode Simulation(MMSIM)的6.2版,在共享許可權安排下納入了Spice、Fast Spice、RF和混合信號仿真器。該方案承諾具有通用的網表和模型集成數據庫,允許設計師從一種仿真引擎切換到另一種,不會產生兼容性問題或編譯問題。

Virtuoso MMSIM套件內的仿真器據稱也得到很大增強。例如,Spectre電路仿真器添加了優化引擎,比傳統的Spice仿真器性能改進3倍,而且增強的Monte Carlo分析也減少了10倍的仿真。

Spectre XL添加了面向RF電路的增強型頻域多速率諧波平衡引擎;面向非線性電路的時域“shooting”算法;用于噪音和抖動分析的新流程;以及集成的模擬、RF和IC仿真功能。

新版本承諾縮短有大量差分信號的設計開發時間達60%。新版Allegro平臺預計6月發布。

Allegro.jpg (94.5 KB)

2009-1-5 23:37

1,安裝軟件,一路next,完全安裝,確定。

2,將《allegro.bat》《 NOLIC.COM》《 choice 》和《雙擊破解》拷貝到X:\Cadence\SPB_16.2 下,同時將NOLIC.COM拷貝到C:\WINDOWS\system32下。

3,確認allegro.bat中沒有以下代碼:

cd %CDSROOT%\tools\Capture

nolic

nolic

cd %CDSROOT%\tools\pspice

nolic

nolic

如果有,將它們刪除。

4,雙擊《雙擊破解》,多運行幾次,至到沒有錯誤出現。

5,用UltraEdit或WinHex打開\capture目錄下的capture.exe文件,還有\pspice目錄下的immgr.exe、pspiceaa.exe、pspice.exe、stmed.exe、psp_eng.dll、Magnetic Parts Editor.exe、modeled.exe七個文件,在2進制下查找字串“00 83 C4 0C 8B 45 F8 8B E5 5D C3 55 8B EC 81 EC 84 01 00 00 57 C7 45 F8 00 00 00 00 C7 45 F4 ”,將“55 8B EC” 修改為“33 C0 C3”,保存文件,記住:有一個simsetup.dll的文件一定不能修改,否則仿真的功能就會不全!!!

6,用記事本新建一個空文件,命名為license.dat,放在X:\Cadence\SPB_16.2下.

7,新建環境變量LM_LICENSE_FILE,指向X:\Cadence\SPB_16.2\license.dat

8,破解完成!

9,安裝hotfix12.每次安裝完hotfix后都要再重新破解一下

注意:個別殺毒軟件報告nolic.com有病毒,屬于正常,如nod32。因為nolic要修改allegro的可執行文件,運行時最好暫時關閉殺毒軟件。

]]>

本版本包括一些新增功能和互連密度的改進,如剛柔布線,擴展的高密度互連(HDI)規則、PCB的三維(3D)顯示與RF電路的非對稱避讓。拓展的微孔疊層規則允許用戶創建極為復雜的HDI設計,而與柔性板輪廓吻合的多線式曲形總線布線會加快剛柔設計。此外,集成的3D PCB瀏覽器讓設計師可以看到元件與HDI微導孔內部,從而為機械設計團隊消除了不必要的迭代。Allegro PCB RF選件還通過使用一個或多個RF元件的非對稱避讓幫助工程師加快創建精確RF電路的速度。

“我們參與了16.3版本的多個階段的測試,對其印象非常深刻,” Kaleidescape Canada公司高級PCB設計師Vincent Di Lello說。“這個新版本的改良很好地解決了我們的小型化設計問題,我們期待著這個新版本發布后能夠盡快將其應用于我們的設計流程中。”

新版Allegro與OrCAD使用多階段預發布的方式確保內容與質量能夠符合客戶的需要。來自北美、歐洲、亞洲和日本的20多家客戶參與了多階段測試計劃。參與測試計劃的客戶與Cadence的合作伙伴包括NVIDIA、Emerson、Kaleidescape、Freedom CAD、NordCAD、FlowCAD、Graser與Tektronix。

16.3版本中還包含對OrCAD系列產品應用效率與可用性的一系列大幅改良。例如OrCAD Capture CIS如今提供了自動布線功能以迅速增加連線,還有全新的三維封裝顯示功能。OrCAD PCB Editor提供了三維查看與“翻板”設計/編輯以及單面PCB設計的跳線支持。OrCAD Signal Explorer有一個經改良的用戶界面,有拖拽和復制粘貼功能,有前后關聯的右擊功能并支持本地IBIS模型。

可用性改進是新版Allegro PCB信號與電源完整性軟件的又一個重點,它提供了一個全新的用戶界面,并為預布線分析環境增加了疊層感知功能。通過對本地IBIS與SPICE模型包括Cadence Virtuoso? Spectre? 電路仿真模型的支持, I/O緩沖器建模標準也包含在其中。另外一個改進設計周期管理的地方是能夠用大量吉比特級信號快速掃描PCB,并且迅速確定應該在哪里進行詳細分析,信號會根據其信噪比進行排列。

“這個最新版Allegro有很多的改進,能夠解決剛性或剛柔設計上的小型化設計問題,”Freedom CAD首席運營官Scott Miller說。“作為一家設計服務公司,我們一直很有興趣提高我們設計師的效率和設計周期的可預測性。我們將會轉移到16.3版本,也推薦我們的客戶盡快轉移。”

該版本解決的另外一些重要問題是與部件數據管理有關。集成的ECAD、MCAD部件創建,生成與發布可以降低不必要的原型機出樣次數。這個新部件導入功能可以擴展預發布與臨時部件的管理與通知,縮短設計周期。此外,工程師可以通過使用批準的與推薦的部件替換原來的部件來實現自動部件更新,也可以通過廢棄部件跟蹤以確保產品的質量。

Allegro與OrCAD PCB Design 16.3版將于2009年12月初開始向客戶提供下載。

]]>都面臨著如何將手頭的Protel設計移植到Cadence PCB設計軟件中的問題。

在這個過程當中碰到的問題大致可分為兩種:一是設計不很復雜,設計師只想借助Cadence CCT的強大自動布線功能完成布線工作;二是設計復雜,設計師需要借助信噪分析工具來對設計進行信噪仿真,

設置線網的布線拓撲結構等工作。

對于第一種情況,要做的轉化工作比較簡單,可以使用Protel或Cadence提供的Protel到CCT的轉換工具來完成這一工作。對于第二種情況,要做的工作相對復雜一些,下面將這種轉化的方法作一簡單的介紹。

Cadence信噪分析工具的分析對象是Cadence Allegro的brd文件,而Allegro可以讀入合乎其要求的第三方網表,Protel輸出的Telexis格式的網表滿足Allegro對第三方網表的要求,這樣就可以將Protel文件注入Allegro。

這里有兩點請讀者注意。首先,Allegro第三方網表在$PACKAGE段不允許有“.”;其次,在Protel中,我們用BasName[0:N]的形式表示總線,用BasName[x]表示總線中的一根信號,Allegro第三方網表中總線中的一根信號的表示形式為Bas NameX,讀者可以通過直接修改Protel輸出的Telesis網表的方法解決這些問題。

Allegro在注入第三方網表時還需要每種類型器件的設備描述文件Device.txt文件,它的格式如下:

Package: package type

Class: classtype

Pincount: total pinnumber

Pinused: ...

其中常用的是PACKAGE,CLASS,PINCOUNT這幾項。PACKAGE描述了器件的封裝,但Allegro在注入網表時會用網表中的PACKAGE項而忽略設備描述文件中的這一項。CLASS確定器件的類型,以便信噪分折,Cadence將器件分為IC,IO,DISCRETE三類。PINCOUNT說明器件的管腳數目。對于大多數器件,Device.txt文件中包含有這三項就足夠了。

有了第三方網表和設備描述文件,我們就可以將Protel中原理圖設計以網表的形式代入到Cadence PCB設計軟件中,接下來,設計師就可以借助Cadence PCB軟件在高速高密度PCB設計方面的強大功能完成自己的設計。

]]>

由Taray公司開發,Cadencer的客戶可通過原始設備供應商(OEM)協議獲得,這一獨一無二的聯合解決方案提供了優化的correct-by-constructionFPGA引腳分配,它可使PCB布線過程中減少引腳優化迭代次數,同時減少將FPGA整合PCB設計所需的層數。Allegro FPGA System Planner通過FPGA引腳自動分配,還縮短了公司應用FPGA在PCB系統上模擬ASIC的時間。

“我嘗試了其它承諾簡化FPGA I/O復雜性問題的工具,但沒有一個有象Taray公司這樣的解決方法,”Harris公司GCSD信號完整TMT負責人Roberto Cordero說道,“Taray公司的FPGA I/O綜合技術是惟一一個能讓我們在系統級輸入我們的設計意圖的,它完全自動將引腳分配一次整合到多個FPGA中。Taray公司的技術將成為Cadence公司產品一個強有力的組合。”

對于日益增長的數據吞吐量以及越來越多的功能,其產品導致大量引腳數的FPGA具有具有高速IO的需求。這些FPGAs還具有更高級的存儲器接口、更低的功耗,從而解決客戶對開發更加“綠色”的產品需要。使用這種更大容量、更多功能和先進高速接口的FPGA,在PCB系統中、以及在PCB上使用FPGA進行ASIC.模擬的數目正在增加。 Cadence公司OrCAD和Allegro FPGA System Planner面向那些將FPGA用于PCB系統而面臨挑戰的系統公司和IC公司。

“現成的多FPGA原型板并不總是能滿足設計師的要求,”Xilinx公司硅硬件與應用資深總監Ed McGettigan說道,“使用這種FPGA I/O綜合技術,設計者可創造出一個新的原型系統,同時比使用標準的引腳優化手工方式快得多的時間找出多種互聯與組件的設計方法。”

該技術在一系列可擴展解決方案中均可獲得,從OrCAD FPGA System Planner到Allegro FPGA System Planner L, XL 以及GXL,并與OrCAD Capture, OrCAD PCB Designer,Allegro Design Entry HDL 和 Allegro PCB Design產品緊密整合。FPGA System Planner縮減了將FPGA整合到PCB的時間,通過FPGA資源的最佳化使用,增強了FPGA的性能,并通過減少密集布局、復雜和大量引腳數的 FPGA所需的PCB層數從而降低了PCB的生產成本。

“Cadence 公司的FPGA System Planner一個創新的解決方案,面向那些面臨將現今大量引腳數目、復雜的FPGA整合到PCB設計流程挑戰的設計團隊”Cadence公司副總栽Charlie Giorgetti,說道,“這正是我們的客戶期待從我們這里獲得的能夠縮短PCB上有大量引腳數目的FPGA的設計周期并降低管理風險的那種技術、自動化和創新。