─│’wąąŲ„░l╔õŪ░Ż¼ąĶ£yįć’wąąŲ„Ė„ĒŚģóöĄŻ¼ģóöĄ£yįć╩Ū═©▀^öĄō■ėøõøŲ„ėøõø’wąąŲ„öĄō■▓óé„ų┴Ąž├µ£yįć┼_ĪŻ£yįć▀^│╠ųąŻ¼×ķ┴╦▒ŻūC£yįć╚╦åT╚╦╔Ē░▓╚½Ż¼’wąąŲ„║═Ąž├µ£yįć┼_ķgŠÓąĶėą300 mŻ¼ā╔š▀ķg▓╔ė├ķLŠĆöĄō■é„▌öĪŻ¼FėąĄ─╝╝ągėąŻ║RSę╗485┐éŠĆŻ¼į┌Äū░┘├ūĢrŻ¼é„▌ö╦┘Č╚▌^Ą═Ż╗CAN┐éŠĆļmŠ▀ėą▌^Ė▀Ą─┐╔┐┐ąįŻ¼Ą½é„▌ö╦┘Č╚ę▓▌^Ą═Ż╗Č°Ū¦šūęį╠½ŠWĮė┐┌Ą─é„▌ö╦┘Č╚║▄┐ņŻ¼Ą½ęį╠½ŠWģfūhÅ═ļsŻ¼▓╗▀mė├ĪŻ×ķ┤╦Ż¼▀@└’╠ß│÷ę╗ĘN╗∙ė┌

FPGA║═

LVDSĮė┐┌Ų„╝■Ą─╣Ō└|é„▌ö╝╝ągĪŻ

ĪĪĪĪ2 LVDS║åĮķ

ĪĪĪĪĄ═ļŖē║▓ŅĘųą┼╠¢(Low Voltage Differential SignalingŻ¼║åĘQLVDS)╩Ūę╗ĘN▀mæ¬Ė▀╦┘öĄō■é„▌öĄ─═©ė├³cī”³c╬’└ĒĮė┐┌╝╝ągĪŻ╦³▓╔ė├Ą═ö[Ę∙▓ŅĘųą┼╠¢╝╝ągŻ¼╩╣Ųõą┼╠¢─▄į┌▓ŅĘųPCBŠĆī”ā║╗“ŲĮ║ŌļŖ└|╔ŽęįÄū░┘MbŻ»sĄ─╦┘Č╚é„▌öŻ«ŲõĄ═ö[Ę∙║═Ą═ļŖ┴„“īäė▌ö│÷īŹ¼FĄ═įļ┬Ģ║═Ą═╣”║─ĪŻ

ĪĪĪĪ├┐éĆ³cĄĮ³c▀BĮėĄ─▓ŅĘųī”ā║ė╔“īäėŲ„Īó╗ź▀BŲ„║═Įė╩šŲ„ĮM│╔ĪŻ“īäėŲ„║═Įė╩šŲ„ų„ę¬═Ļ│╔TTLą┼╠¢║═LVDSą┼╠¢ų«ķgĄ─▐DōQĪŻ╗ź▀BŲ„░³║¼ļŖ└|ĪóPCB╔Ž▓ŅĘųŠĆī”ā║ęį╝░Ųź┼õļŖūĶĪŻLVDS“īäėŲ„ė╔ę╗éĆ“īäė▓ŅĘųŠĆī”ā║Ą─ļŖ┴„į┤ĮM│╔Ż¼LVDSĮė╩šŲ„Š▀ėąĖ▀▌ö╚ļūĶ┐╣Ż¼ę“┤╦“īäėŲ„▌ö│÷Ą─ļŖ┴„┤¾▓┐ĘųČ╝┴„Įø100”ĖĄ─Ųź┼õļŖūĶŻ¼▓óį┌Įė╩šŲ„Ą─▌ö╚ļČ╦«a╔·╝s350 mVĄ─ļŖē║ĪŻ«ö“īäėŲ„ĘŁ▐DīóĖ─ūā┴„ĮøļŖūĶĄ─ļŖ┴„ĘĮŽ“Ż¼ę“┤╦«a╔·ėąą¦Ą─▀ē▌ŗ1║═▀ē▌ŗOĄ─Ą═ö[Ę∙“īäėą┼╠¢īŹ¼FĖ▀╦┘▓┘ū„▓ó£pąĪ╣”║─Ż¼▓ŅĘųą┼╠¢╠ß╣®▀m«öįļ┬Ģ▀ģŠēĪŻ▓╗╣▄╩╣ė├Ą─╩ŪPCBŠĆī”ā║▀Ć╩ŪļŖ└|Ż¼Č╝▒žĒÜĘ└ų╣Ę┤╔õŻ¼£p╔┘ļŖ┤┼Ė╔ö_ĪŻLVDSę¬Ū¾╩╣ė├ę╗ų╗┼cĮķ┘|ŽÓŲź┼õĄ─ĮKČ╦ļŖūĶŻ¼æ¬īóŲõ▒M┐╔─▄Ąž┐┐Į³Įė╩šŲ„Ę┼ų├ĪŻLVDSĮė╩šŲ„┐╔ęį│ą╩▄1 VĄ─“īäėŲ„┼cĮė╩šŲ„ķgī”ĮėĄžĄ─ļŖē║▓ŅĪŻė╔ė┌LVDS“īäėŲ„Ąõą═Ą─Ų½ų├ļŖē║×ķ1Ż«2 VŻ¼╦∙ęįŲõļŖē║▓Ņ“īäėŲ„Ąõą═Ą─Ų½ų├ļŖē║ęį╝░▌pČ╚±Ņ║Žįļ┬Ģų«║═ĘČć·×ķ0Ż«2Ī½2Ż«2 VĪŻĮ©ūhĮė╩šŲ„Ą─▌ö╚ļļŖē║ĘČć·×ķ0Ī½2Ż«4 VĪŻ

ĪĪĪĪ3 ┐é¾wįOėŗĘĮ░Ė

ĪĪĪĪŽĄĮyįOėŗę¬Ū¾é„▌ö╦┘Č╚æ¬į┌1~16 MbŻ»sūįäė▀mæ¬Ż¼é„▌öŠÓļx▓╗ąĪė┌300 mŻ¼Ūę▒žĒÜ┼cŲõ╦¹ŽĄĮyļŖ┤┼Ė¶ļxŻ¼▒▄├ŌļŖ┤┼Ė╔ö_ĪŻę“┤╦Ż¼įōŽĄĮyįOėŗ▓╔ė├╝»│╔Ą─LVDSĮė┐┌Ų„╝■DS92LVl021Ż¼ŲõöĄō■é„▌ö╦┘Č╚╩Ū1*0 MbŻ»sŻ¼10╬╗öĄō■╬╗ĪŻČ°CLC001Ż¼CLC012×ķīŻė├ķLŠĆļŖ└|“īäėŲ„Ż¼┼c╣Ō─ŻēKŽÓĮY║Ž┐╔īóé„▌öŠÓļxöUš╣2 kmŻ¼Ūę═Ō▓┐ļŖ┬Ę║åå╬Ż¼╣”║─Ą═ĪŻFPGA▀xė├Spartanę╗2ŽĄ┴ąŲ„╝■Ż¼ŲõūŅĖ▀╣żū„╦┘Č╚×ķ200 MHzŻ¼▀ē▌ŗ║Ļå╬į¬žSĖ╗Ż¼ØMūŃŽĄĮyįOėŗę¬Ū¾ĪŻę“┤╦Ż¼įōŽĄĮyįOėŗ▀xė├LVDSĮė┐┌Ų„╝■īŹ¼FLVDSķLŠĆé„▌öŻ¼Č°ėøõøŲ„Īó£yįć┼_║═LVDSŲ„╝■Įė┐┌Ą─Ģrą“Ųź┼õät▀xė├FPGAīŹ¼FĪŻ

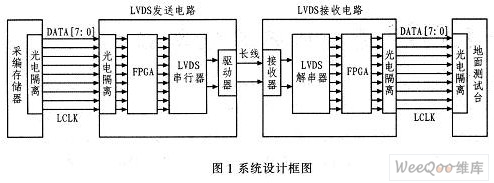

ĪĪĪĪłD1×ķŽĄĮyįOėŗĄ─┐“łDŻ¼£yįć┼_░l╦═Ą─STATEĪóCTLlĪóCTL2Ą╚ĀŅæB╝░┐žųŲą┼╠¢é„╦═ų┴ėøõøŲ„Ż¼▓óīóėøõøŲ„░l╦═Ą─öĄō■╝░═¼▓ĮĢrńŖé„╦═ų┴Ąž├µ£yįć┼_ĪŻŲõųąŻ¼ėøõøŲ„ĪóLVDS░l╦═Č╦ĪóLVDSĮė╩šČ╦Ą─ļŖį┤Š∙ė╔£yįć┼_╠ß╣®Ż¼ļŖē║×ķ+9 VĪŻ

ĪĪĪĪLVDSķLŠĆé„▌ö─ŻēKĘų×ķLVDS░l╦═ļŖ┬Ę║═LVDSĮė╩šļŖ┬ĘĪŻLVDS░l╦═ļŖ┬ĘīóÅ─ėøõøŲ„Įė╩šĄĮĄ─▓óąąöĄō■▀Mąą╦┘Č╚Ųź┼õ║¾▐DōQ│╔LVDS┤«ąąöĄō■┴„Ż¼▓ó═©▀^ļpĮgŠĆ░l╦═ĪŻLVDSĮė╩šļŖ┬ĘīóĮė╩šĄĮĄ─LVDS┤«ąąöĄō■┴„▀ĆįŁ│╔▓óąąöĄō■▀Mąą╦┘Č╚Ųź┼õ║¾╦═ų┴£yįć┼_ĪŻ

ĪĪĪĪ4 ė▓╝■įOėŗ

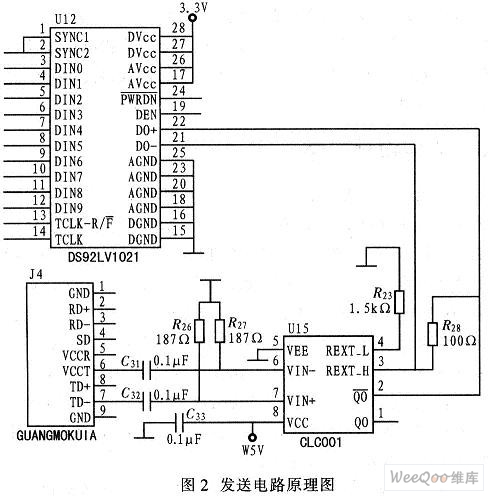

ĪĪĪĪįōŽĄĮyįOėŗĄ─ĻPµI▓┐Ęų×ķLVDSĄ─Įė┐┌įOėŗŻ¼ė╔ė┌é„▌ööĄō■╦┘Č╚║▄Ė▀Ż¼ę“┤╦æ¬░┤ššĖ▀╦┘ļŖ┬ĘĄ─ę¬Ū¾▀MąąįOėŗŻ¼╦∙ėą▓╝ŠĆæ¬▒M┴┐Č╠Ż¼é„▌öŠĆ┬ĘūĶ┐╣Ųź┼õĪŻé„▌ö─ŻēK░l╦═Č╦╣żū„Ģr╩ūŽ╚ė╔FPGAĮoDS92LV1021Ą─╩╣─▄Č╦DEN╝░TCLK-RŻ»Fė|░lčž▀xō±Ė▀ļŖŲĮŻ¼▓óŽ“TCLKę²─_▌ö│÷20 MHzĄ─╣żū„ĢrńŖŻ¼Įėų°DS92LV1021īóÅ─FPGA╠ÄĮė╩šĄĮĄ─TTL▓óąąą┼╠¢▐DōQ×ķLVDSś╦£╩Ą─┤«ąąą┼╠¢Ż¼į┘ė╔Doę╗╝░Do+▌ö│÷ų┴CLC001“īäėŲ„Ż¼ĮøļŖ╣Ō▐DōQ║¾Ż¼ė╔╣Ō└|é„▌öų┴Įė╩š░ÕļŖ┬ĘŻ¼▓óė╔Įė╩šļŖ┬ĘĄ─╣ŌļŖ▐DōQŲ„╦═ų┴CLC012Ż¼Å─Č°čaāöęč╦ź£pĄ─ą┼╠¢Ż¼į┘ė╔DS92LV1212ĮŌ┤«Ų„▀ĆįŁ│÷10╬╗▓óąąöĄō■╝░l╬╗ĢrńŖ╬╗ĪŻłD2×ķ░l╦═ļŖ┬ĘįŁ└ĒłDĪŻ

ĪĪĪĪé„▌ö─ŻēKĮė╩šČ╦ų„ę¬ė╔CLC012Š∙║ŌŲ„╝░DS92LV1212ĮŌ┤«Ų„ĮM│╔ĪŻDS92LV1212Ą─D00~D09īó▀ĆįŁ│÷Ą─▓óąąöĄō■▌ö│÷Ż¼RCLK×ķ▀ĆįŁ│÷Ą─═¼▓ĮĢrńŖŻ¼REFCLK×ķĮŌ┤«Ų„Ą─╣żū„ĢrńŖŻ¼ė╔FPGAĮo│÷ĪŻ

ĪĪĪĪ5 ▄ø╝■įOėŗ

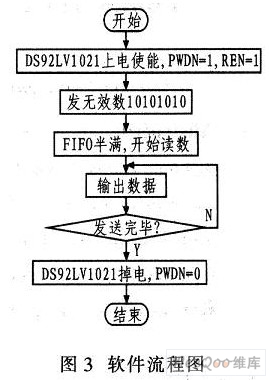

ĪĪĪĪŽĄĮy╔ŽļŖ║¾Ż¼£yįć┼_Ž╚Ž“▓╔ŠÄŲ„░l│÷ūxöĄ├³┴ŅŻ¼▓╔ŠÄŲ„ĮėĄĮ├³┴Ņ║¾Ż¼ęįl MbŻ»sĄ─╦┘Č╚▌ö│÷8╬╗▓óąąöĄō■Ż¼Č°LVDSé„▌öŲ„╝■ūŅĄ═╣żū„╦┘Č╚×ķ16 MbŻ»sŻ¼×ķ┴╦īŹ¼F╦┘Č╚Ųź┼õ┼cūį▀mæ¬Ż¼įōŽĄĮyįOėŗ▓╔ė├┴╦Soatan-2Eą═FPGAā╚▓┐ļp┐┌RAMīŹ¼FFIFOŻ¼ŲõĢrńŖūŅĖ▀╣żū„Ņl┬╩×ķ200 MHzŻ¼ØMūŃę¬Ū¾Ż¼«ö▓╔ŠÄŲ„ęį1 M bŻ»s╦┘Č╚▌ö│÷öĄō■ĢrŻ¼╩ūŽ╚▀M╚ļFPGAā╚▓┐FIFOŻ¼FPGAā╚▓┐ī”öĄō■ėŗöĄŻ¼«ö┤µØM512éĆöĄ║¾Ż¼FPGAęį20 MbŻ»sĄ─╦┘Č╚▌ö│÷8╬╗▓óąąöĄō■Ż¼×ķ┴╦▒ŻūCDS92LVl021ę╗ų▒╠Äė┌╣żū„ĀŅæBŻ¼FPGAį┌ā╔┤╬░l╦═öĄō■Ą─ķgą¬╦∙▌ö│÷Ą─¤oą¦öĄŻ¼ėąą¦öĄ║═¤oą¦öĄ═©▀^LVDSé„▌öŲ„╝■Ą─lO╬╗öĄō■╬╗Ą─Ė▀2╬╗öĄō■╬╗ū„×ķś╦ųŠ╬╗▀Mąąģ^ĘųŻ¼į┌Įė╩šČ╦FPGA═©▀^┼ąöÓś╦ųŠ╬╗üĒūRäeėąą¦öĄ╗“¤oą¦öĄŻ¼╔ߌē¤oą¦öĄŻ¼▒ŻūCöĄō■š²┤_é„▌öĪŻFPGAį┌š¹éĆŽĄĮyųąŲöĄō■ŠÅø_ū„ė├Ż¼ė╔ė┌▓╔ė├FIFOū„×ķ═Ō▓┐öĄō■Įė┐┌Ż¼╦∙ęį┐╔īŹ¼Fī”═Ō▓┐öĄō■Ą─ūį▀mæ¬ę¬Ū¾ĪŻš¹éĆ│╠ą“ė├VHDLšZčįŠÄīæŻ¼┴„│╠łD╚ńłD3╦∙╩ŠĪŻ

ĪĪĪĪ6 įć“×ĮY╣¹

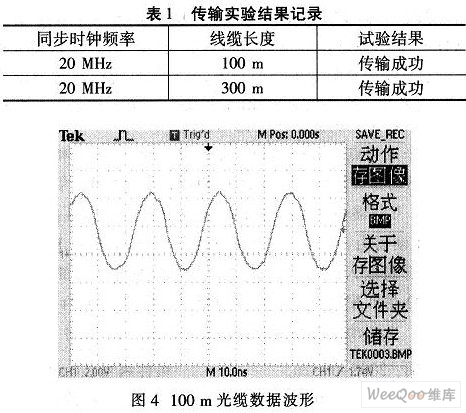

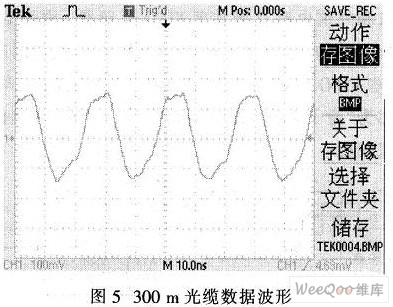

ĪĪĪĪ×ķ┴╦£yįćūŅĮKą¦╣¹Ż¼į┌░l╦═ļŖ┬Ę║═Įė╩šļŖ┬Ęų«ķgė├▓╗═¼ķLČ╚Ą─å╬─Ż╣Ō└w▀BĮėŻ¼ŽĄĮy╔ŽļŖ║¾Ż¼░l╦═Č╦░l╦═öĄō■╦┘Č╚×ķ20 MbŻ»sŻ¼╩╣ė├╩Š▓©Ų„▓Č½@Įė╩šČ╦öĄō■▓©ą╬Ż¼▓ó▀Mąąī”▒╚Ż¼īŹ“×ĮY╣¹ėøõø╚ń▒Ē1╦∙┴ąĪŻłD4║═łD5ĘųäeĮo│÷100 m║═300 m╣Ō└|Ą─öĄō■▓©ą╬ĪŻė╔öĄō■▓©ą╬łDų¬Ż¼į┌é„▌ö▀^│╠ųąŻ¼▓©ą╬╗¹ūāĘŪ│ŻąĪŻ¼ø]ėą│÷¼Fš`┤a║═üGöĄĄ─¼FŽ¾Ż¼═Ļ╚½ØMūŃŽĄĮyę¬Ū¾ĪŻ

ĪĪĪĪ7 ĮYšZ

╝ė║├ėč

╝ė║├ėč  ░lČ╠ą┼

░lČ╠ą┼

Post ByŻ║2010-11-19 11:36:32

Post ByŻ║2010-11-19 11:36:32

╝ė║├ėč

╝ė║├ėč  ░lČ╠ą┼

░lČ╠ą┼

Post ByŻ║2010-12-4 21:36:42

Post ByŻ║2010-12-4 21:36:42