TMS320C54x╩Ū─┐Ū░Ųš▒ķ╩╣ė├Ą─Č©³c(di©Żn)DSPąŠŲ¼ĪŻ╦³Ą─╠ž³c(di©Żn)╩Ū╣”║─║▄Ą═Ż©į┌100MIPSĢr(sh©¬)×ķ60mW),┐╔ė├ė┌öĄ(sh©┤)ūųĘõĖC═©ą┼ĪóéĆ(g©©)╚╦═©ą┼ŽĄĮy(t©»ng)Īóīż║¶ÖC(j©®)ĪóéĆ(g©©)╚╦öĄ(sh©┤)ūųų·└Ē(PDA)ĪóATMŻ©«É▓Įé„▌ö─Ż╩ĮŻ®Į╗ōQÖC(j©®)ĪóöĄ(sh©┤)ūų¤o(w©▓)ŠĆ═©ą┼Īóš{(di©żo)ųŲĮŌš{(di©żo)Ų„Ą╚ŅI(l©½ng)ė“ĪŻłD1▒Ē╩Š┴╦C54xĄ─░l(f©Ī)š╣▀^(gu©░)│╠╝░æ¬(y©®ng)ė├ŅI(l©½ng)ė“ĪŻ

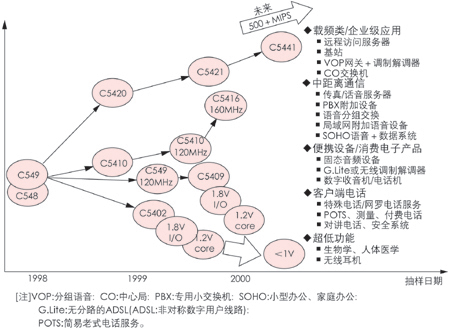

łD1 TMS320C5000ąį─▄░l(f©Ī)š╣?f©żn)Ņør╝░æ¬(y©®ng)ė├ŅI(l©½ng)ė“

TMS320ŽĄ┴ąĄ─═¼ę╗┤·ąŠŲ¼Š▀ėąŽÓ═¼Ą─CPUĮY(ji©”)śŗ(g©░u),Ą½Ė∙ō■(j©┤)╩ął÷(ch©Żng)Ą─▓╗═¼ąĶę¬,ą╬│╔ą┬Ą─┤µā”(ch©│)Ų„┼c═ŌįO(sh©©)Ą─▓╗═¼ĮM║Ž,«a(ch©Żn)╔·┴╦ČÓĘN┼╔╔·Ų„╝■ĪŻ

TMS320C54xĻP(gu©Īn)µI╠žąį

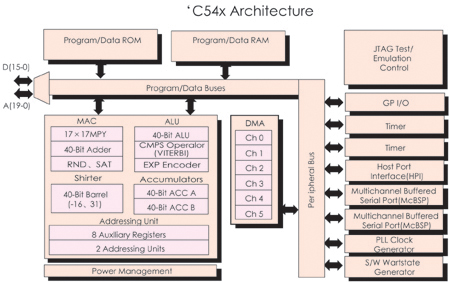

łD2╩ŪC54x╣”─▄ĮY(ji©”)śŗ(g©░u)łD,╦³Ą─ų„ꬹį─▄╚ńŽ┬Ż║

łD2 TMS320C54x╣”─▄ĮY(ji©”)śŗ(g©░u)┐“łD

ó▒ CPU

Ž╚▀M(j©¼n)Ą─ČÓ┐éŠĆĮY(ji©”)śŗ(g©░u)Ż║ę╗ĮM│╠ą“┐éŠĆŻ©PABĪóPBŻ®,╚²ĮMöĄ(sh©┤)ō■(j©┤)┐éŠĆŻ©CABĪóCB,DABĪóDB,EABĪóEBŻ®

40╬╗Ą─öĄ(sh©┤)īW(xu©”)▀ē▌ŗå╬į¬Ż©ALUŻ®Ż║░³└©40╬╗Ą─═░ą╬ęŲ╬╗╝─┤µŲ„║═ā╔éĆ(g©©)¬Ü(d©▓)┴óĄ─40╬╗└█╝ėŲ„

17 17╬╗▓óąą│╦Ę©Ų„║═40╬╗īŻė├╝ėĘ©Ų„,å╬ų▄Ų┌═Ļ│╔│╦Ę©/└█╝ė(MAC)

▀mė┌Viterbi▀\(y©┤n)╦ŃĄ─▒╚▌^Īó▀xō±Īó┤µā”(ch©│)å╬į¬Ż©CSSUŻ®

ųĖöĄ(sh©┤)ŠÄ┤aŲ„,┐╔į┌å╬ų▄Ų┌ā╚(n©©i)ėŗ(j©¼)╦ŃŻ©40╬╗Ż®└█╝ėŲ„ųąöĄ(sh©┤)ųĄĄ─ųĖöĄ(sh©┤)

ā╔éĆ(g©©)ĄžųĘ«a(ch©Żn)╔·Ų„,░³└©░╦éĆ(g©©)▌oų·╝─┤µŲ„║═ā╔éĆ(g©©)Ą─╦Ńąg(sh©┤)å╬į¬

ó▓ ┤µā”(ch©│)Ų„

┐╔īżųĘ┤µā”(ch©│)┐šķg▀_(d©ó)192KūųŻ©│╠ą“ĪóöĄ(sh©┤)ō■(j©┤)╝░I/OĖ„64 64bitŻ®,C548▀Ć┐╔öU(ku©░)š╣│╠ą“┤µā”(ch©│)Ų„Ż©8šūūųŻ®

Ąõą═C5400ąŠŲ¼┤µā”(ch©│)Ų„

ó│ Ų¼ā╚(n©©i)═ŌįO(sh©©)

▄ø╝■┐╔ŠÄ│╠Ą╚┤²ĀŅæB(t©żi)«a(ch©Żn)╔·Ų„

┐╔ŠÄ│╠Ą─ēKĮ╗ōQ

Ų¼ā╚(n©©i)µiŽÓŁh(hu©ón)Ģr(sh©¬)ńŖ«a(ch©Żn)╔·Ų„

Į¹ų╣═Ō▓┐┐éŠĆĄ─┐žųŲÖC(j©®)ųŲ

ó┤ ųĖ┴Ņ╝»

ųžÅ═(f©┤)å╬ŚlųĖ┴Ņ┼cųžÅ═(f©┤)ųĖ┴ŅēK

&nbs

p; ┤µā”(ch©│)Ų„ēKęŲäė(d©░ng)ųĖ┴Ņ

32╬╗öĄ(sh©┤)▀\(y©┤n)╦ŃųĖ┴Ņ

┐╔═¼Ģr(sh©¬)ūx╚Ī2╗“3éĆ(g©©)▓┘ū„öĄ(sh©┤)Ą─ųĖ┴Ņ

Š▀ėą▓óąą▒Ż┤µ║═▓óąą╝ė▌dĄ─╦Ńąg(sh©┤)ųĖ┴Ņ

Śl╝■▒Ż┤µųĖ┴Ņ

óĄ ╣”║─┐žųŲ

IDLE1ĪóIDLE2║═IDLE3ųĖ┴Ņ┐╔┐žųŲŲõ▀M(j©¼n)╚ļĮĄ╣”║──Ż╩Į

┐╔┐žųŲ╩Ūʱ▌ö│÷CLKOUTą┼╠¢(h©żo)

óČ IEEEś╦(bi©Īo)£╩(zh©│n)Ą─1149.1▀ģĮńÆ▀├Ķ▀ē▌ŗĮė┐┌

TMS320C54xĮY(ji©”)śŗ(g©░u)Ė┼╩÷

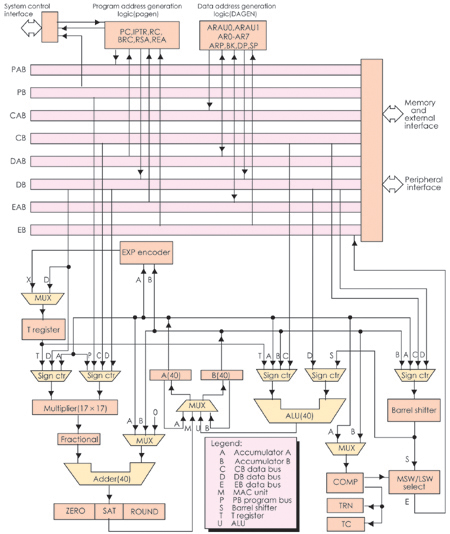

''C54xė╔ųąčļ╠Ä└ĒŲ„CPUĪó┤µā”(ch©│)Ų„║═Ų¼ā╚(n©©i)═ŌįO(sh©©)ĮM│╔,▓╔ė├╣■ĘĮY(ji©”)śŗ(g©░u),ėą¬Ü(d©▓)┴óĄ─│╠ą“┐šķgĪóöĄ(sh©┤)ō■(j©┤)┐šķg║═I/O┐šķgĪŻłD3╩Ū''C54xĄ─ā╚(n©©i)▓┐ė▓╝■┐“łDĪŻ

ī”(du©¼)╦∙ėąĄ─''C54xŲ„╝■üĒ(l©ói)šf(shu©Ł),łDųąŽ┬░ļ▓┐╦∙╩ŠĄ─ųąčļ╠Ä└Ēå╬į¬Ż©CPUŻ®╩Ū═©ė├Ą─ĪŻ

┐éŠĆĮY(ji©”)śŗ(g©░u)

ę╗ĮM│╠ą“┐éŠĆŻ©PABĪóPBŻ®║═╚²ĮMöĄ(sh©┤)ō■(j©┤)┐éŠĆCABĪóCB,DABĪóDB,EABĪóEBŻ®īóā╚(n©©i)▓┐Ė„▓┐╝■┬ō(li©ón)ŽĄŲüĒ(l©ói)ĪŻ

łD3 TMS320C54xā╚(n©©i)▓┐ė▓╝■┐“łD

PB- │╠ą“┐éŠĆ,é„╦═│╠ą“┤·┤a╗“┤µį┌│╠ą“┐šķgĄ─öĄ(sh©┤)ō■(j©┤);

CBĪóDBĪóEB- öĄ(sh©┤)ō■(j©┤)┐éŠĆ,▀BĮėCPUĪóöĄ(sh©┤)ō■(j©┤)ĄžųĘ«a(ch©Żn)╔·▀ē▌ŗĪó│╠ą“ĄžųĘ«a(ch©Żn)╔·▀ē▌ŗĪóŲ¼ā╚(n©©i)═ŌįO(sh©©)╝░┤µā”(ch©│)Ų„Ą╚Ė„▓┐╝■;

CB║═DB- é„╦═Å─┤µā”(ch©│)Ų„ūx│÷Ą─öĄ(sh©┤)ō■(j©┤),╝┤Ī░ūxĪ▒▓┘ū„╩╣ė├Ą─öĄ(sh©┤)ō■(j©┤)┐éŠĆ;

EB-é„╦═Ž“┤µā”(ch©│)Ų„īæ╚ļĄ─öĄ(sh©┤)ō■(j©┤),╝┤"īæ"▓┘ū„╩╣ė├Ą─öĄ(sh©┤)ō■(j©┤)┐éŠĆ;

PABĪóCABĪóDABĪóEAB- Ė„ī”(du©¼)æ¬(y©®ng)Ą─ĄžųĘ┐éŠĆ;

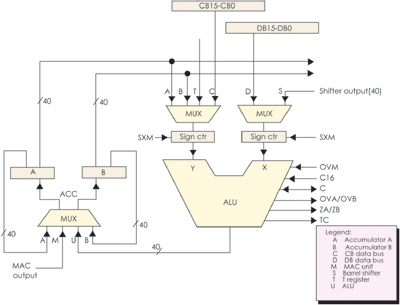

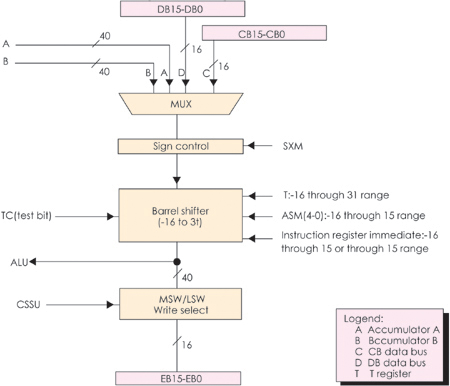

łD4 ALU╣”─▄┐“łD

ųąčļ╠Ä└Ēå╬į¬Ż©CPUŻ®

ALUŻ║╦Ńąg(sh©┤)▀ē▌ŗ▀\(y©┤n)╦Ńå╬į¬

ų„ę¬ė╔40╬╗ALU║═ā╔éĆ(g©©)40╬╗└█╝ėŲ„(ACCA║═ACCB)ĮM│╔,╚ńłD4╦∙╩ŠĪŻ

&

nbsp; ALU║═ā╔éĆ(g©©)└█╝ėŲ„ė├üĒ(l©ói)═Ļ│╔40╬╗Č■▀M(j©¼n)ųŲča(b©│)┤aĄ─╦Ńąg(sh©┤)▀\(y©┤n)╦Ń,ę▓─▄═Ļ│╔▓╝Ā¢▀\(y©┤n)╦ŃĪŻ«ö(d©Īng)ĀŅæB(t©żi)╝─┤µā”(ch©│)Ų„ST1Ą─C16╬╗ų├1Ģr(sh©¬),┐╔ū÷ā╔éĆ(g©©)16╬╗ALU,═¼Ģr(sh©¬)═Ļ│╔ā╔éĆ(g©©)16╬╗▀\(y©┤n)╦ŃĪŻ

▌ö╚ļŻ║

16╬╗┴ó╝┤öĄ(sh©┤);

üĒ(l©ói)ūįöĄ(sh©┤)ō■(j©┤)┤µā”(ch©│)Ų„Ą─16╬╗öĄ(sh©┤);

üĒ(l©ói)ūįĢ║┤µŲ„TĄ─16╬╗öĄ(sh©┤);

üĒ(l©ói)ūįöĄ(sh©┤)ō■(j©┤)┤µā”(ch©│)Ų„ūx│÷Ą─ā╔éĆ(g©©)16╬╗öĄ(sh©┤);

üĒ(l©ói)ūįöĄ(sh©┤)ō■(j©┤)┤µā”(ch©│)Ų„ūx│÷Ą─ę╗éĆ(g©©)32╬╗öĄ(sh©┤);

üĒ(l©ói)ūį└█╝ėŲ„Ż©A║═BŻ®Ą─40╬╗öĄ(sh©┤);

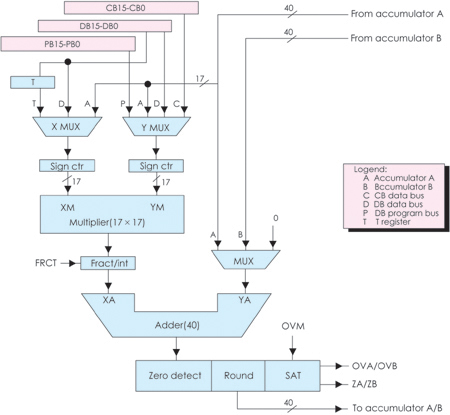

łD5 ═░ą╬ęŲ╬╗Ų„╣”─▄┐“łD

▌ö│÷Ż║ALUĄ─40╬╗▌ö│÷▒╗╦══∙└█╝ėŲ„A╗“BĪŻ

łD6 │╦/╝ė─ŻēK╣”─▄ĘĮ┐“łD

═░ą╬ęŲ╬╗Ų„Ż║īó▌ö╚ļöĄ(sh©┤)ō■(j©┤)ū¾ęŲ0Ī½31╬╗╗“ėęęŲ0Ī½16╬╗,Įø(j©®ng)│Żė├ū„öĄ(sh©┤)ūųČ©ś╦(bi©Īo)Īó╬╗╠ß╚ĪĪóöU(ku©░)š╣╦Ńąg(sh©┤)║═ęń│÷▒Żūo(h©┤)Ą╚▓┘ū„ĪŻ ▌ö╚ļ40╬╗Ż║üĒ(l©ói)ūį└█╝ėŲ„╗“Įø(j©®ng)DBĪóCBĄ─ öĄ(sh©┤)ō■(j©┤)┤µā”(ch©│)Ų„;

▌ö│÷40╬╗Ż║▀BĄĮALU╗“Įø(j©®ng)EB▀BĄĮöĄ(sh©┤)ō■(j©┤)┤µā”(ch©│)Ų„;

╦∙ęŲ╬╗öĄ(sh©┤)ė╔ųĖ┴ŅųąęŲ╬╗ūųČ╬ĪóST1Ą─ASMūųČ╬╗“T╝─┤µŲ„ųĖČ©ęŲ╬╗╬╗öĄ(sh©┤)øQČ©ĪŻ

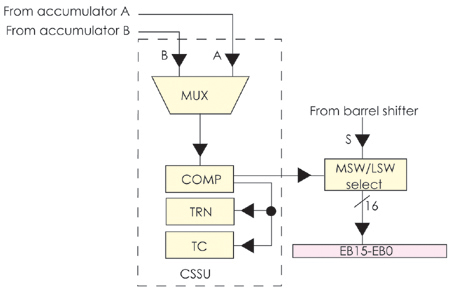

łD7 ▒╚▌^Īó▀xō±┼c▒Ż┤µå╬į¬Ż©CSSUŻ®╣”─▄┐“łD

│╦/╝ė─ŻēKŻ║ė╔│╦Ę©Ų„Īó╝ėĘ©Ų„Īó▌ö╚ļöĄ(sh©┤)ō■(j©┤)Ą─Ę¹╠¢(h©żo)┐žųŲ▀ē▌ŗĪóąĪöĄ(sh©┤)┐žųŲ▀ē▌ŗĪó┴ŃÖz£y(c©©)Īó╔ß╚ļĪóęń│÷/’¢║═▀ē▌ŗ║═16╬╗Ģ║┤µ╝─┤µŲ„TĄ╚ĮM│╔ĪŻ│╦Ę©Ų„║═ALUį┌ę╗éĆ(g©©)ųĖ┴Ņų▄Ų┌ā╚(n©©i)╣▓═¼═Ļ│╔(17 17ča(b©│)┤a)│╦/╝ėŻ©40╬╗Ż®▀\(y©┤n)╦Ń,Ūę┐╔▓󹹥žū„ALU▀\(y©┤n)╦Ń,▀@ą®╣”─▄┐╔ė├üĒ(l©ói)ū÷EuclideanŠÓļx╝░LMS×V▓©Ą╚Å═(f©┤)ļs▀\(y©┤n)╦ŃĪŻ│╦/╝ė─ŻēK╣”─▄ĘĮ┐“łD╚ńłD6╦∙╩ŠĪŻ

▒╚▌^Īó▀xō±┼c▒Ż┤µå╬į¬(CSSU)Ż║┐╔ęį═Ļ│╔└█╝ėŲ„Ą─Ė▀╬╗ūų║═Ą═╬╗ūųų«ķgĄ─ūŅ┤¾ųĄ▒╚▌^(CMPSųĖ┴ŅŻ®ĪŻ┴Ēę╗╣”─▄╩Ū└¹ė├ā×(y©Łu)╗»Ą─Ų¼ā╚(n©©i)ė▓╝■┘Yį┤═Ļ│╔öĄ(sh©┤)ō■(j©┤)═©ą┼Īó─Ż╩ĮūR(sh©¬)äeĄ╚ŅI(l©½ng)ė“ųąĮø(j©®ng)│Żė├ĄĮĄ─ViterbiĄ¹ą╬▀\(y©┤n)╦ŃĪŻ

&

nbsp;

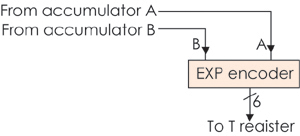

łD8 ųĖöĄ(sh©┤)ŠÄ┤aŲ„

ųĖöĄ(sh©┤)ŠÄ┤aŲ„Ż║ė├ė┌ų¦│ųå╬ų▄Ų┌ųĖ┴ŅEXPĄ─īŻė├ė▓╝■,╚ńłD8╦∙╩ŠĪŻ

└█╝ėŲ„ųąöĄ(sh©┤)ųĄĄ─ųĖöĄ(sh©┤)ųĄ,ęįČ■▀M(j©¼n)ųŲča(b©│)┤aą╬╩Į(-8Ī½31)┤µĘ┼ė┌Ģ║┤µŲ„Tųą;

CPUĀŅæB(t©żi)║═┐žųŲ╝─┤µŲ„Ż║

''C54x╣▓ėą3éĆ(g©©)16╬╗ĀŅæB(t©żi)║═┐žųŲ╝─┤µŲ„Ż©PMSTĪóST0ĪóST1Ż®╦³éāČ╝╩Ū┤µā”(ch©│)Ų„ė│Ž¾╝─┤µŲ„,┐╔ęįĘĮ▒ŃĄžīæ╚ļöĄ(sh©┤)ō■(j©┤)Īó╗“ė╔öĄ(sh©┤)ō■(j©┤)┤µā”(ch©│)Ų„ī”(du©¼)╦³éā╝ė▌dĪŻ

ā╚(n©©i)▓┐┤µā”(ch©│)Ų„

Īż''C54xĄ─┤µā”(ch©│)Ų„Ęų×ķ╚²éĆ(g©©)┐╔¬Ü(d©▓)┴ó▀xō±Ą─┐šķgŻ║│╠ą“┐šķgĪóöĄ(sh©┤)ō■(j©┤)┐šķg║═I/O┐šķg;

Īż''C54xĄ─Ų¼ā╚(n©©i)┤µā”(ch©│)Ų„░³└©ROM║═RAM,ŲõųąRAMėų┐╔Ęų×ķSARAM║═DARAMŻ║SARAM×ķå╬īżųĘ╝─┤µā”(ch©│)Ų„,DARAM×ķļpīżųĘ╝─┤µā”(ch©│)Ų„(ę╗ų▄Ų┌ā╚(n©©i)┐╔ęįįLå¢(w©©n)ā╔┤╬)ĪŻ

ROMę╗░Ń┼õų├│╔│╠ą“┤µā”(ch©│)┐šķg,ė├ė┌┤µĘ┼ꬳ╠(zh©¬)ąąĄ─ųĖ┴ŅĪóŽĄöĄ(sh©┤)▒ĒĄ╚╣╠Č©▓┘ū„öĄ(sh©┤)ĪŻę▓┐╔ęį▓┐ĘųĄž░▓┼┼ĄĮöĄ(sh©┤)ō■(j©┤)┤µā”(ch©│)┐šķg,ė╔PMSTĄ─ĀŅæB(t©żi)╬╗ ║═DROMøQČ©;RAM ę╗░Ń░▓┼┼ĄĮöĄ(sh©┤)ō■(j©┤)┤µā”(ch©│)┐šķg,┤µĘ┼ł╠(zh©¬)ąąųĖ┴Ņ╦∙ę¬ė├Ą─öĄ(sh©┤)ō■(j©┤)ĪŻĄ½ę▓┐╔ęį░▓┼┼ĄĮ│╠ą“┐šķg,ė╔PMSTĄ─ĀŅæB(t©żi)╬╗OVLYøQČ©ĪŻ▓╗═¼''C54xŽĄ┴ąā╚(n©©i)▓┐┤µā”(ch©│)Ų„┼õų├Ė„▓╗ŽÓ═¼ĪŻ

''C54xĄ─īżųĘĘĮ╩Į

TMS320C54xĄ─ųĖ┴Ņ┐╔─▄║¼ėą1éĆ(g©©)┤µā”(ch©│)Ų„▓┘ū„öĄ(sh©┤)Ż©ųĖ┴Ņšf(shu©Ł)├„ųąė├Smem▒Ē╩ŠŻ®,ę▓┐╔─▄ėą2éĆ(g©©)┤µā”(ch©│)Ų„▓┘ū„öĄ(sh©┤)Ż©ųĖ┴Ņšf(shu©Ł)├„ųąė├XmemĪóYmem▒Ē╩ŠŻ®,ĘųäeĘQ×ķå╬┤µā”(ch©│)Ų„▓┘ū„öĄ(sh©┤)║═ļp┤µā”(ch©│)Ų„▓┘ū„öĄ(sh©┤)ĪŻå╬┤µā”(ch©│)Ų„▓┘ū„öĄ(sh©┤)ėą7ĘNīżųĘĘĮ╩Į,╦³éā╩ŪŻ║

┴ó╝┤īżųĘŻ║ ▓┘ū„öĄ(sh©┤)(│ŻöĄ(sh©┤))║¼į┌ųĖ┴Ņųą;

Į^ī”(du©¼)īżųĘŻ║ ųĖ┴Ņųą║¼ėą▓┘ū„öĄ(sh©┤)Ą─16╬╗ĄžųĘ;

└█╝ėŲ„īżųĘŻ║ ▓┘ū„öĄ(sh©┤)ĄžųĘį┌└█╝ėŲ„ųą(A);

ų▒ĮėīżųĘŻ║ ųĖ┴Ņųą║¼ėą▓┘ū„öĄ(sh©┤)ĄžųĘĄ─Ą═7 ╬╗;

ķgĮėīżųĘŻ║ ▓┘ū„öĄ(sh©┤)Ą─ĄžųĘį┌▌oų·╝─┤µŲ„ųą,ų¦│ųĄ╣╬╗ą“?q©▒)żųĘĪó裣h(hu©ón)īżųĘĄ╚╣”─▄;

┤µā”(ch©│)Ų„ė│Ž±Ą─╝─┤µŲ„īżųĘŻ║

įLå¢(w©©n)┤µā”(ch©│)Ų„ė│Ž±╝─┤µŲ„,

ėų▓╗ė░ĒæDP╗“SP;

Č茯īżųĘŻ║ įLå¢(w©©n)Č茯;

ļp┤µā”(ch©│)Ų„▓┘ū„öĄ(sh©┤)ų¦│ųę╗ą®╠ž╩ŌųĖ┴ŅŻ║

╚ńMACĪóFIRĄ╚Å═(f©┤)ļsųĖ┴ŅĪŻ

''C54xĄ─┴∙╝ē(j©¬)ųĖ┴Ņ┴„╦«ŠĆ

&nb

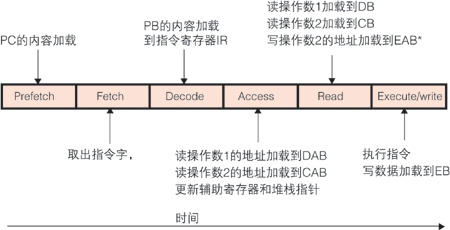

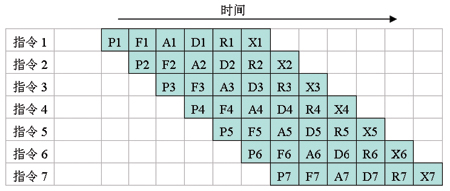

sp; ''C54x CPUĄ─ųĖ┴Ņ┴„╦«ŠĆėą┴∙╝ē(j©¬),├┐éĆ(g©©)ų▄Ų┌ėą┴∙ŚlųĖ┴Ņį┌╣żū„,╦³éā╠Äė┌š¹éĆ(g©©)ł╠(zh©¬)ąą▀^(gu©░)│╠Ą─▓╗═¼ļAČ╬,╚ńłD9╦∙╩ŠĪŻ

łD9 ┴„╦«ŠĆ▓╗═¼╣żū„ļAČ╬▓┘ū„ā╚(n©©i)╚▌

┴„╦«ŠĆĄ─╣żū„╚½▓┐×ķå╬ūųųĖ┴Ņ▀B└m(x©┤)ł╠(zh©¬)ąąĢr(sh©¬)Ż©└ĒŽļŪķørŻ®╚ńłD10 ╦∙╩ŠĪŻ

łD10 ┴„╦«ŠĆš²│Ż╣żū„Ģr(sh©¬)ū÷śI(y©©)Ūķør

ėęÖ┌

ėęÖ┌

╝ė║├ėč

╝ė║├ėč  ░l(f©Ī)Č╠ą┼

░l(f©Ī)Č╠ą┼

Post ByŻ║2010-11-22 9:02:08

Post ByŻ║2010-11-22 9:02:08